# A 0.07 mm<sup>2</sup> 2.2 mW 10 GHz Current-Reuse Class-B/C Hybrid VCO Achieving 196-dBc/Hz FoM<sub>A</sub>

Md. Tawfiq Amin, Jun Yin, Member, IEEE, Pui-In Mak, Senior Member, IEEE, and Rui P. Martins, Fellow, IEEE

Abstract—This Letter describes a current-reuse class-B/C hybrid voltage-controlled oscillator (VCO) with robust startup, enhanced phase noise and differential balancing at small area and power. Specifically, an asymmetrical CMOS class-C core is aided by a symmetrical NMOS-only class-B core that effectively shares the bias current for deeper class-C operation of the former; wider margin of startup against PVT variations, and lower amplitude imbalance against oscillation frequencies. Moreover, this topology adds the freedom of adjustable peak dynamic current and boosts the oscillation swing at low power. The spiral inductors with patterned ground shields shrink the die size. Fabricated in 65 nm CMOS, the 0.07 mm<sup>2</sup> VCO prototype exhibits 10.15-to-11.17 GHz tunability, and -107.73-dBc/Hz phase noise at 1 MHz offset, while dissipating merely 2.2 mW at 1.2 V. The achieved area-included figure-of-merit (FoM<sub>A</sub> = 196 dBc/Hz) favorably compares with the state-of-the-art.

*Index Terms*—Current-reuse, CMOS, class-B, class-C, phase noise, startup, voltage-controlled oscillator (VCO).

## I. INTRODUCTION

V OLTAGE controlled oscillator (VCO) is still one of the most area-and-power-hungry blocks of nanoscale CMOS wireless transceivers. In fact, it is challenging to realize an ultracompact VCO while still keeping state-of-the-art phase noise and power consumption, as a small inductor intrinsically results in lower LC tank's impedance that in return demands a larger bias current to secure an adequate output swing [1].

Compared with the conventional class-B LC-VCOs using an NMOS-/PMOS-only cross-coupled pair, the CMOS currentreuse class-B VCO [Fig. 1(a)] can halve the bias current while offering the same negative transconductance and output swing, being an attractive approach to save the power [2]. Yet, CMOS current-reuse VCO is architecturally asymmetrical, rendering its differential balancing sensitive to the peak dynamic current

Manuscript received January 13, 2015; revised February 11, 2015; accepted April 03, 2015. Date of publication May 22, 2015; date of current version July 02, 2015. This work was supported by the University of Macau (MYRG2015-00097-AMSV) and Macao Science and Technology Development Fund (FDCT)—SKL fund.

M. T. Amin, J. Yin, and P.-I. Mak are with the State-Key Laboratory of Analog and Mixed-Signal VLSI, and Faculty of Science and Technology Electrical and Computer Engineering Department, University of Macau, Macao, China. (e-mail: pimak@umac.mo).

R. P. Martins is with the State-Key Laboratory of Analog and Mixed-Signal VLSI and Faculty of Science and Technology—ECE Department, University of Macau, Macao, China, and also with the Instituto Superior Técnico, Universidade de Lisboa, Lisboa 1049–001, Portugal (e-mail: rmartins@umac.mo).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LMWC.2015.2427582

$V_{out} \leftarrow U_{tank} \leftarrow U_{urrent} \\ V_{out} \leftarrow V_{une} \leftarrow V_{out} \leftarrow$

Fig. 1. Current-reuse VCO: (a) class-B [2] and (b) class-C with an adaptive bias scheme [6].

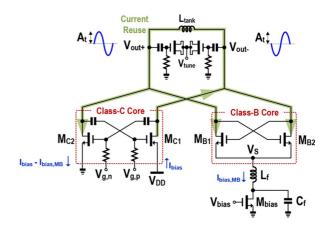

Fig. 2. Proposed current-reuse class-B/C hybrid VCO.

in the period when both  $M_1$  and  $M_2$  are switched on. Thus, extra source or drain resistors [2], [3], or cascaded PMOS and NMOS transistors [4], [5], are required to limit the peak dynamic current in order to prevent  $M_1$  and  $M_2$  from entering into the deep triode region. To eliminate those extra components while reducing the power, [6] reported a CMOS current-reuse class-C VCO with an adaptive bias scheme [Fig. 1(b)] to aid the startup and output differential balancing through an undistorted dynamic current. Good balancing was only demonstrated over a narrow frequency tuning range (FTR) of 2.2%.

This Letter proposes a current-reuse class-B/C hybrid VCO as shown in Fig. 2. Besides to ensure the startup of the class-C core by adding a class-B cross-coupled pair [7], this design also features: 1) a CMOS current-reuse class-C core to reduce the power consumption while still maintaining a good phase noise, and 2) improved balancing of the differential outputs over a reasonably wide FTR with the help of a balanced class-B cross- coupled pair. Interactively, the class-B cross-coupled pair also facilitates the class-C core to operate in the current-limited

1531-1309 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications standards/publications/rights/index.html for more information.

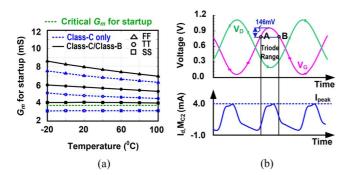

Fig. 3. Simulated (a) small signal  $G_m$  versus temperature at different process corners (SS, TT, FF), and (b) transient waveforms of the gate and drain voltages and drain current of  $M_{C2}$ .

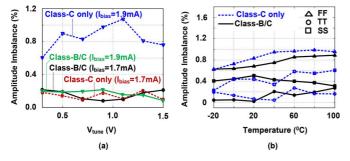

Fig. 4. Simulated amplitude imbalance of the class-C only and class-B/C VCOs against (a)  $V_{tune}$  and (b) temperature at different process corners.

region, resulting in a larger output swing that further reduces phase noise.

## II. PROPOSED CURRENT-REUSE CLASS-B/C HYBRID VCO

For a class-B/C hybrid VCO, the steady-state performance is dominated by the class-C core that should consume most of the bias current. Thus, current-reuse is particularly effective for the class-C core. Recalling Fig. 2, the CMOS transconductor  $M_{\rm C1}$  ( $g_{\rm mc1}$ , 40/0.06  $\mu$ m) and  $M_{\rm C2}$  ( $g_{\rm mc2}$ , 14/0.06  $\mu$ m) should be asymmetrical in dimensions to counteract their differences in process parameters. Ideally, the gate bias  $V_{g,p}$  and  $V_{g,n}$ have to be set lower than the device's threshold voltage for deeper class-C operation. This act however leads to a small negative transconductance worsening the startup robustness (i.e., failed to oscillate against PVT variations and long startup time). As a result, by paralleling the asymmetrical class-C with a symmetrical class-B using an NMOS-only cross-coupled pair ( $M_{\rm B1}$  and  $M_{\rm B2}$  with  $g_{\rm mB}$ ), the effective negative transconductance  $(-G_m)$  can be balanced better and boosted to  $-G_m = -(g_{mc1} || g_{mc2} + g_{mB}/2)$  for robust startup.

The primary concern of a current-reuse VCO is to operate it in the current-limited region as the voltage-limited region will directly result in asymmetrical differential outputs. Moreover, in the voltage-limited region, the device's conduction angle is wider, penalizing the DC-to-RF current-conversion efficiency. In the current-limited region,  $V_{g,n}$  and  $V_{g,p}$  have to be chosen such that both  $M_{C1}$  and  $M_{C2}$  remain in saturation. The maximum single-ended oscillation amplitude  $(A_t)$  is thus limited by (assuming the same common voltage):  $A_t < (V_{g,p} - V_{g,n} + |V_{th,p}| + V_{th,n})/4$ , where  $V_{th,p}(V_{th,n})$  denotes the threshold voltage of  $M_{C1}(M_{C2})$ .  $A_t$  can be maximized by increasing the voltage difference between  $V_{g,p}$  and  $V_{g,n}$ . Yet, when considering the differential balancing,  $V_{g,p}$  and  $M_{C2}$ . Here, with the design freedom provided by the class-B core,  $V_{g,n}$  can be re-

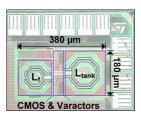

Fig. 5. Chip photo of the proposed VCO fabricated in 65 nm CMOS.

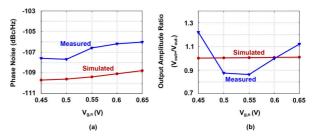

Fig. 6. Simulated and measured (a) phase noise, and (b) amplitude ratio as a function of  $V_{g,n}$  when  $V_{g,p}$  is fixed at 0.6 V.

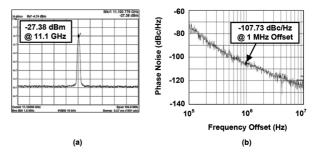

Fig. 7. Measured (a) output spectrum and (b) phase noise.

duced comfortably for differential balancing, while boosting the oscillation swing for better phase noise.

The theoretical output amplitude of the current-reuse class-B/C VCO is  $[(2/\pi)I_{\text{bias,MB}} + (I_{\text{bias}} - I_{\text{bias,MB}}) + I_{\text{bias}}]R_P$ , where  $R_{\rm p}$  is the parallel resistance of the LC tank,  $I_{\rm bias}$  is the total bias current and  $I_{\text{bias,MB}}$  is the bias current diverted into  $M_{\rm B1,2}$  (10/0.06  $\mu$ m). Since the current efficiency of the class-B core is only 63.7% of that of the class-C core [7], the choice of  $I_{\rm bias,MB}$  is a trade-off between the power efficiency and robust startup. In this design,  $I_{\rm bias,MB}$  is chosen as 30% of  $I_{\rm bias}$ for reliable startup against PVT variations. Fig. 3(a) shows the simulated small-signal  $G_m$  at different process corners (SS, TT, FF) and over a wide range of temperature (-20 to)100°C) for both the class-C-only VCO and the current-reuse class-B/C VCO under the same bias current. The critical  $G_m$ for startup (3.6 mS) is marked. Thanks to the added class-B core, the current-reuse class-B/C VCO can safely meet the startup conditions for process corners and temperature, while the class- C only VCO fails to startup at the SS corner.

The transient waveforms of the gate and drain voltages and drain current of  $M_{C2}$  are plotted in Fig. 3(b). When carrying the maximum current, the NMOS is slightly pushed out of the saturation region with a maximum  $V_{gs} - V_{th,n} - V_{ds} = 0.146$  V. Yet, the transient current waveforms are still effectively in class-C for all operational current levels.

For the class-B core, in order to reduce the phase noise introduced by the tail transistor  $M_{\text{bias}}$ , it is upsized appropriately to minimize its flicker noise. Furthermore, the inductor  $L_f$  is employed to resonate with  $C_f$  at twice the VCO oscillation frequency  $(f_{\text{osc}})$  as shown in Fig. 2. From simulations, a very small

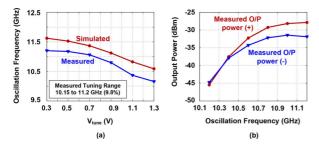

Fig. 8. (a) Simulated and measured FTR. (b) Measured output powers.

TABLE I

COMPARISON WITH THE STATE-OF-THE-ART

|                                                                                                                                                                                       | [1]<br>MWCL'07    | [4]<br>MWCL'08    | [6]<br>RFIC'13               | [9]<br>ASSCC'12                 | This<br>Work                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------------------|---------------------------------|--------------------------------|

| Technology                                                                                                                                                                            | 180 nm            | 180 nm            | 180 nm                       | 65 nm                           | 65 nm                          |

| Topology                                                                                                                                                                              | Current-<br>Reuse | Current-<br>Reuse | Class-C<br>Current-<br>Reuse | Ac-coupled<br>Current-<br>Reuse | Class-B/C<br>Current-<br>Reuse |

| f <sub>osc</sub> (GHz)                                                                                                                                                                | 2.4               | 16                | 4.6                          | 2.53                            | 11.2                           |

| FTR (%)                                                                                                                                                                               | 13.7              | 5.6               | 2.2                          | 29                              | 9.6                            |

| Power (mW)                                                                                                                                                                            | 0.97              | 8.1               | 2.4                          | 0.28                            | 2.2                            |

| PN @ 1 MHz<br>(dBc/Hz)                                                                                                                                                                | -111              | -111              | -118 #                       | -112#                           | -107.73                        |

| Die Area (mm <sup>2</sup> )                                                                                                                                                           | 0.47*             | 0.15*             | 0.18                         | 0.13                            | 0.07                           |

| FoM 1 (dBc/Hz)                                                                                                                                                                        | 179               | 187               | 187                          | 185                             | 185                            |

| FoM <sub>A<sup>2</sup></sub> (dBc/Hz)                                                                                                                                                 | 182               | 195               | 194                          | 194                             | 196                            |

| FoM <sub>T</sub> <sup>3</sup> (dBc/Hz)                                                                                                                                                | 182               | 181               | 174                          | 194                             | 185                            |

| # Normalized from original measured data * Estimated core area<br><sup>1</sup> FoM = 10 log <sub>10</sub> $\left( \left( \frac{f_{OSC}}{4S} \right)^2 \frac{1}{P_{OSC}} \right) - PN$ |                   |                   |                              |                                 |                                |

$1 \text{ FoM} = 10 \log_{10} \left( \left( \frac{\Delta f}{\Delta f} \right) \frac{P_{\text{diss}}(\text{mW})}{P_{\text{diss}}(\text{mW})} \right) - P_{\text{IN}}$

${}^{2}$  FoM<sub>A</sub> = FoM<sup>1</sup> - 10 log<sub>10</sub>[Area(mm<sup>2</sup>)],  ${}^{3}$  FoM<sub>T</sub> = FoM<sup>1</sup> - 20 log<sub>10</sub>  $\left[\frac{FTR}{10}\right]$

inductance of 0.4 nH is adequate to reduce the phase noise by 7 dB (3 dB) at 10 kHz (1 MHz) offset.

Fig. 4(a) plots the simulated amplitude imbalance against the frequency tuning voltage  $(V_{tune})$  at different bias currents, which are set by changing  $V_{g,p}$  and  $V_{g,n}$ . For a lower bias current of 1.7 mA, the amplitude imbalance for both class-C only and class- B/C VCOs are < 0.22%. However, when the bias current goes up to 1.9 mA, the amplitude imbalance for the class-B/C VCO is still kept the same, while that for the class-C only VCO is degraded to 1.1%. Transistor and capacitor mismatches also can affect the differential balancing. At  $I_{\text{bias}} =$ 1.7 mA and  $V_{\text{tune}} = 0.3$  (1.2) V, Monte Carlo simulations show that the mean of amplitude imbalance is 0.14% (0.7%) for the class-B/C VCO, and 1.6% (1.4%) for the class-C only VCO. Fig. 4(b) gives the simulated amplitude imbalance over temperature at 3 process corners. The worst amplitude imbalance for the class-B/C VCO is 0.9% at 100°C, under the FF process corner. This shows that class-B/C VCO has robust differential balancing against frequency, bias and process variations.

# **III. MEASUREMENT RESULTS**

The proposed VCO targets a 10 GHz  $f_{\rm osc}$  and ~10% FTR. It was fabricated in a standard ST 65 nm CMOS process without any ultra-thick metals. The die area of the *LC* tank is minimized by choosing a small inductor of 0.8 nH with a patterned ground shield, which has a simulated Q of ~5. Fig. 5 shows the chip photo of the VCO occupying a small die size of 380 × 180  $\mu$ m<sup>2</sup>. During the measurements,  $V_{\rm g,n}$  and  $V_{\rm g,p}$  are kept constant when the VCO starts up. Fig. 6 depicts the measured phase noise and amplitude ratio versus  $V_{\rm g,n}$  when  $V_{\rm g,p}$  is fixed

at 0.6 V. It can be seen that  $V_{g,n} = 0.5$  V allows the low phase noise at low power consumption with a reliable startup, even with a sub-optimum amplitude imbalance ratio. Thus,  $V_{g,n}$ and  $V_{g,p}$  are set at 0.5 and 0.6 V, respectively, for other measurements. The VCO consumes 2.2 mW at a 1.2 V supply. At 11.1 GHz, the measured output power is -27.38 dBm as shown in Fig. 7(a) via an open-drain test buffer. The phase noise at 1 and 10 MHz offsets are -107.73 and -123 dBc/Hz, respectively, as depicted in Fig. 7(b). The FTR is from 10.15 to 11.17 GHz (9.6%) when  $V_{tune}$  changes from 0.3 to 1.2 V as shown in Fig. 8(a). Fig. 8(b) shows the measured output power at the two differential output terminals as a function of  $V_{\text{tune}}$ . The power discrepancy at higher frequency should be due to the impedance mismatch of the bondwire and PCB traces (consistent with  $\sim 10\%$  mismatch in their parasitic capacitances, from simulations). For more accurate measurements of the amplitude imbalance, a better EM model and on-chip downconversion mixer might be added to downconvert the signal to low frequency first, such that the effect of mismatch at the output ports can be minimized [8]. Table I summarizes the results and compares this work with the relevant art using current-reuse and class-C techniques [1], [4], [6], [9]. This work attains comparable figure-of-merits (FoMs), particularly the area-included  $FoM_A$  of 196 dBc/Hz.

## IV. CONCLUSION

This Letter reported a 65 nm CMOS 10 GHz current-reuse class-B/C hybrid VCO achieving a state-of-the-art performance in a small die area of 0.07 mm<sup>2</sup>. The key technique is to parallel an asymmetrical current-reuse class-C core with a symmetrical class-B core that effectively shares the bias current for a deeper class-C operation of the former, while improving the startup condition, differential balancing and oscillation swing. The achieved phase noise is -107.73 dBc/Hz at 1 MHz offset while drawing only 2.2 mW at 1.2 V. The achieved FoM, FoM<sub>A</sub> and FoM<sub>T</sub> are 185, 196 and 185 dBc/Hz, respectively.

#### References

- S.-H. Lee, S. L. Jang, Y.-H. Chuang, J. J. Chao, J.-F. Lee, and M. H. Juang, "A low power injection locked LC-tank oscillator with current reused topology," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 3, pp. 220–222, Mar. 2007.

- [2] S.-J. Yun, S.-B. Shin, H.-C. Choi, and S.-G. Lee, "A 1 mW currentreuse CMOS differential LC-VCO with low phase noise," in *Proc. IEEE Int. Solid-State Circuit Conf.*, Feb. 2005, pp. 540–541.

- [3] Z. Wang, H. S. Savci, and N. S. Dogan, "1-V ultra-low-power CMOS LC VCO for UHF quadrature signal generation," in *Proc. ISCAS*, May 2006, pp. 4022–4025.

- [4] C. Yang and Y. Chiang, "Low phase-noise and low-power CMOS VCO constructed in current-reused configuration," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 2, pp. 136–138, Feb. 2008.

- [5] M. Wei, S. Chang, and S. Huang, "An amplitude-balanced currentreused CMOS VCO using spontaneous transconductance match technique," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 6, pp. 395–397, Jun. 2009.

- [6] T. Siriburanon, W. Deng, K. Okada, and A. Matsuzawa, "A currentreuse class-C LC-VCO with an adaptive bias scheme," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, May 2013, pp. 35–38.

- [7] L. Fanori, A. Liscidini, and P. Andreani, "A 6.7-to-9.2 GHz 55 nm CMOS hybrid class-B/class-C cellular TX VCO," *IEEE ISSCC Dig. Tech. Papers*, pp. 354–356, Feb. 2012.

- [8] U. Decanis, A. Ghilioni, E. Monaco, A. Mazzanti, and F. Svelto, "A mm-wave quadrature VCO based on magnetically coupled resonators," *IEEE ISSCC Dig. Tech. Papers*, pp. 280–281, Feb. 2011.

- [9] M. Taghivand, M. Ghahramani, and M. P. Flynn, "A low voltage sub 300 µW 2.5 GHz current reuse VCO," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Nov. 2012, pp. 369–372.