## $0.0045~mm^2$ 15.8 $\mu W$ three-stage amplifier driving 10x-wide (0.15–1.5 nF) capacitive loads with >50° phase margin

Zushu Yan, Pui-In Mak<sup>⊠</sup>, Man-Kay Law and Rui Paulo Martins

> A three-stage amplifier employing embedded capacitor-multiplier compensation (ECMC) and active parallel compensation (APC) to enhance the area efficiency when driving nF-range capacitive loads  $(C_{\rm I})$  is presented. Unlike the conventional current-buffer Miller compensation, ECMC applied to the dominant compensation path saves substantial power and area, while securing a large gain-bandwidth product. The created left-half-plane zero also benefits the phase margin (PM). For the APC, unlike the traditional passive parallel compensation, this work benefits from the Miller effect to avoid the area-consuming resistor, and reduces the entailed capacitances without lowering the parasitic pole position. A multi-path  $G_{\mathrm{m}}$ -boosting second stage enhances the effective transconductance and DC gain. With  $0.0045 \text{ mm}^2$  of area and  $15.8 \,\mu\text{W}$  of power, the  $0.18 \,\mu\text{m}$ CMOS three-stage amplifier measures 1.13 MHz unity-gain frequency,  $0.41~{

> m V/\mu s}$  average slew rate and  $56.2^{\circ}~{

> m PM}$  at 1 nF  $C_{

> m L}$ . Stable responses with >50° PM are attained for a  $10 \times$  range of  $C_L$  from 0.15 to 1.5 nF. The achieved figure-of-merit accounting for both die area and power compares favourably with the state of the art.

Introduction: For flat-panel-display applications that demand thousands of buffer amplifiers [1], three-stage amplifiers have been continuously evolved for better small-/large-signal performances, area efficiency and  $C_{\rm L}$  drivability [2, 3]. However, they suffer from inherent drawbacks. The amplifier in [2] is managed to balance power efficiency and  $C_{\rm L}$  drivability, but area-hungry passive components are entailed to boost the current buffer's transconductance and generate the desired left–right-plane (LHP) zero. The design in [3] relies on an extra local feedback loop (LFL) [2] to move up the parasitic poles in the LHP zero circuit, but the LFL stability becomes very sensitive to the parasitics, and passive components are still unavoidable.

This Letter describes the techniques to realise an ultra-area-efficient  $nF-C_L$  three-stage amplifier. It benefits from the combinatorial effects of embedded capacitor-multiplier compensation (ECMC), active-parallel compensation (APC) and multi-path  $G_m$  boosting technique to optimise the performance.

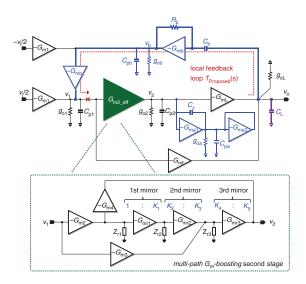

Fig. 1 Proposed three-stage amplifier

*Topology:* The proposed three-stage amplifier is depicted in Fig. 1. The CBMC in the dominant LFL [2] is replaced by an embeddable CM to realise ECMC; its small-signal behaviour is characterised by  $R_{\rm b}$ ,  $C_{\rm b}$ , and two  $G_{\rm mb}$  stages, whereas  $g_{\rm ob}$  and  $C_{\rm pb}$  are the output conductance and parasitic capacitance, respectively. The two  $G_{\rm m1}$  stages represent the differential inputs. Part of the  $-v_i/2$  input signal travelling through the above  $G_{\rm m1}$  leaks to  $v_{\rm o}$  via  $R_{\rm b}$  and  $C_{\rm b}$  which is in-phase with the other  $-v_i/2$  and  $v_i/2$  signals passing the main gain stages. The in-phase sum of these signals creates a useful LHP zero. The second stage is non-

inverting characterised by  $G_{\rm m2\_eff}$ . It is a new multi-path  $G_{\rm m}$ -boosting structure to enhance the transconductance and DC gain with high power efficiency. The feedforward stage  $G_{\rm mf}$  with  $G_{\rm mL}$  forms a pushpull output stage to improve the large-signal behaviour. The APC is attached at  $v_2$ . Alternatively, it can be positioned at  $v_1$ , but practical considerations for pushing up the parasitic pole created by the APC renders the connection of APC at  $v_2$  better. Note that when locating APC at  $v_1$ , the  $(G_{\rm mal}+G_{\rm ma2})/(C_{\rm p1}+C_{\rm pa})$  pole is lower than  $(G_{\rm ma1}+G_{\rm ma2})/(C_{\rm p2}+C_{\rm pa})$  if located at  $v_2$  because  $C_{\rm p1}>C_{\rm p2}$ :  $G_{\rm m1}$  is loaded by  $G_{\rm m2\_eff}$  and  $G_{\rm mf}$  while  $G_{\rm m2\_eff}$  is only loaded by  $G_{\rm mL}$ ;  $G_{\rm mL}$  ( $G_{\rm mf}$ ) is typically implemented by an NMOS (PMOS) device.

LFL analysis and transfer functions: LFL analysis is an insightful method guiding the pole-zero placements [2]. With the assumptions: (i) the DC gain of all the stages is >> 1; (ii)  $C_{\rm pl,2}$ ,  $C_{\rm pa,b} << C_{\rm b,z} << C_{\rm L}$ ; (iii)  $g_{\rm ob} < 1/R_{\rm b} < G_{\rm mb}$ , the LFL transfer function of the amplifier is given by

$$T_{\text{Proposed}}(s) \simeq \frac{-sG_{\text{m2\_eff}}G_{\text{mL}}(G_{\text{mb}}R_{\text{b}} - 1)C_{\text{b}}}{g_{01}g_{02}g_{0\text{L}}(1 + (s/\omega_{\text{p1}}))(1 + (s/\omega_{\text{p2}}))} \times \left[1 + 2\zeta_{\text{CM}}\left(\frac{s}{\omega_{\text{p3}}}\right) + \left(\frac{s}{\omega_{\text{p3}}}\right)^{2}\right] \left(1 + \frac{s}{\omega_{\text{p4}}}\right)$$

(1)

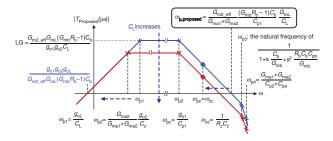

where  $\omega_{\rm p1}$  is  $g_{\rm oL}/C_{\rm L}$ .  $\omega_{\rm p2}$  and  $\omega_{\rm p4}$  associated with ACP are  $(G_{\rm ma2}g_{\rm o2})/[(G_{\rm ma1}+G_{\rm ma2})C_{\rm z}]$  and  $(G_{\rm ma1}+G_{\rm ma2})/(C_{\rm p2}+C_{\rm pa})$ , respectively.  $\zeta_{\rm CM}$  and  $\omega_{\rm p3}$  correspond to the damping factor and natural frequency of the complex poles that are attributed to the embeddable CM. During the derivation, the influence of  $G_{\rm mf}$  is negligible though it slightly shifts the position of the  $G_{\rm ma2}/C_{\rm z}$  zero and introduces another very high-frequency LHP zero; the  $G_{\rm ma2}/C_{\rm z}$  zero has been employed to cancel the  $g_{\rm o1}/C_{\rm p1}$  pole. Consequently, the UGF of the LFL,  $\omega_{\mu,\rm Proposed}$ , is obtained in Fig. 2.

Since  $\omega_{\mu, \text{Proposed}}$  constitutes the first non-dominant pole of the overall transfer function [2], it should be placed at the highest possible frequency while managing to save power. The proposed topology can achieve a large  $\omega_{\mu, Proposed}$  in two power-efficient ways: (i) an extra boosting factor  $(G_{mb1}R_b-1)C_b/C_{p1}$  is introduced when compared with that in [3], reducing the required  $G_{\rm mL}$ ; (ii) the multi-path second-stage  $G_{\rm m2\_eff}$ concurrently reduces the power budget of itself and  $G_{\rm mL}$  while allowing a relatively large  $G_{\rm mal}$  to preserve the LFL stability. As the  $g_{\rm ol}/C_{\rm pl}$  pole is higher than its counterpart in [3], the pole-zero cancellation in the LFL appears at a higher frequency and permits shrinking  $C_z$  for area savings. The variability of  $C_L$  can be assessed by evaluating the LFL gain responses. As illustrated in Fig. 2,  $\omega_{p1}$  decreases when  $C_L$  is increased, while all other poles remain fixed. Since the mid-band LFL gain (LG) is also reduced,  $\omega_{\mu, \mathrm{Proposed}}$  follows. Thus, a large  $C_{\mathrm{L}}$  benefits the LFL stability, but deteriorating the amplifier's PM (i.e. the upper bound of  $C_L$ ). When  $C_L$  is reduced,  $\omega_{\mu,Proposed}$  approaches  $\omega_{p3}$  and  $\omega_{p4}$  degrading the PM of the LFL. Thus, the lower bound of the  $C_L$  is limited by the LFLs PM. The proposed amplifier employs the embeddable CM and APC that can locate their parasitic poles higher than those based on current buffers and/or conventional PC at equal power [2, 3]. The  $C_L$  drivability is therefore extended to smaller values. The transfer function of the amplifier is given by

$$A_{\text{Proposed}}(s) \simeq \frac{A_0(1 + (s/\omega_{z1}))}{(1 + (s/\omega_{\text{pd}}))(1 + (s/\omega_{\mu,\text{Proposed}}))} \times \left[1 + 2\zeta_{\text{CM}} \left(\frac{s}{\omega_{\text{p3}}}\right) + \left(\frac{s}{\omega_{\text{p3}}}\right)^2\right] \left(1 + \frac{s}{\omega_{\text{p4}}}\right)$$

(2)

where  $A_0$  and the dominant pole  $\omega_{\rm pd}$  correspond to  $G_{\rm m1}G_{\rm m2\_eff}G_{\rm mL}/(g_{\rm o1}g_{\rm o2}g_{\rm oL})$  and  $g_{\rm o1}g_{\rm o2}g_{\rm oL}/[G_{\rm m2\_eff}G_{\rm mL}(G_{\rm mb}R_{\rm b}-1)C_{\rm b}]$ , respectively. The GBW is given by  $G_{\rm m1}/(G_{\rm mb}R_{\rm b}-1)C_{\rm b}$ . The LHP zero  $\omega_{\rm z1}=2G_{\rm mb}/[(G_{\rm mb}R_{\rm b}+1)C_{\rm b}]$  counteracts the negative phase shift from the non-dominant poles of  $A_{\rm Proposed}(s)$ , extending the large  $C_{\rm L}$  drivability.

Multi-path  $G_m$ -boosting second stage: Two power-saving ideas are involved to enhance  $G_{\rm m2\_eff}$  and its output resistance: (i) it cascades multiple wideband amplifiers that are realised by small-ratio current mirrors to attain significant transconductance enhancement and (ii) it recycles the current that biases the current mirrors to form a multi-path structure contributing to  $G_{\rm m2\_eff}$ . Unlike the typical single-current-mirror realisation [2, 3], the output resistance of  $G_{\rm m2\_eff}$  here is naturally increased,

as much less current is distributed to the last mirror. Fig. 1 shows the block-diagram model of  $G_{\rm m2\_eff}$  that exploits three-cascaded current mirrors and two feedforward paths. The boosted  $G_{\rm m2\_eff}$  is

$$G_{\text{m2\_eff}} = \left(\frac{K_5}{K_4} \frac{K_3}{K_2} K_1 + K_5\right) G_{\text{m2}} + \frac{K_5}{K_4} G_{\text{m3}}$$

(3)

where  $K_5$  is the ratio of  $G_{\mathrm{m4}}$  to the conductance part of  $Z_{r1}$  that models the input impedance of the first mirror. Although the noise of the current mirrors is also raised by transconductance amplification, the amplifier's noise performance is almost unaffected since the multi-path  $G_{\mathrm{m}}$ -boosting is enforced in the second stage.

Fig. 2 Magnitude responses of LFL T<sub>Proposed</sub>(s)

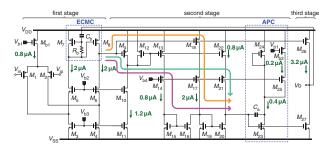

Fig. 3 Schematic of proposed three-stage amplifier

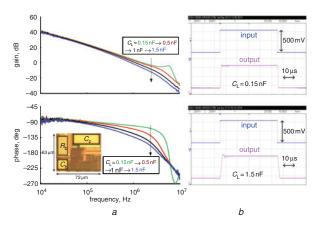

**Fig. 4** Measured performance of 0.18  $\mu$ m CMOS amplifier (inset) a AC responses at  $C_L$  = 0.15, 0.5, 1 and 1.5 nF b 500 mV-step responses at  $C_L$  = 0.15 and 1.5 nF

Schematic: The schematic of the amplifier is shown in Fig. 3. The input stage,  $G_{\rm m1}$ , is realised with a folded cascode transconductor ( $M_1$ – $M_8$  and  $M_{\rm b1}$ ). Together with  $R_{\rm b}$  and  $C_{\rm b}$ ,  $M_{7-8}$  implement the two  $G_{\rm mb}$  stages constituting the embeddable CM.  $M_9$ – $M_{22}$  form the multi-path  $G_{\rm m}$ -boosting stage to implement  $G_{\rm m2\_eff}$ . Highlighted in Fig. 3 are the three signal paths that contribute to  $G_{\rm m2\_eff}$ : (i)  $M_9$  ( $G_{\rm m2}$ ), the PMOS current mirror ( $M_{12-13}$ ) with  $M_{13}$  realising  $G_{\rm mr1}$ ; (ii)  $M_{18}$  ( $G_{\rm m3}$ ) and the mirror ( $M_{19-20}$ ) with  $M_{20}$  being  $G_{\rm mr3}$ , and the two NMOS mirrors ( $M_{15-16}$  and  $M_{19-20}$ ) with  $M_{16}$  implementing  $G_{\rm mr2}$ ; (iii)  $M_9$ , the mirror ( $M_{12-22}$ ) with  $M_{22}$  ( $G_{\rm m4}$ ) recycling  $M_{20}$ 's current. APC is composed of  $M_{23}$ – $M_{25}$ ,  $M_{b2}$  and  $C_z$ .  $M_{23}$  acts as  $G_{\rm mal}$  and  $M_{24}$  plays the role of  $G_{\rm ma2}$ .  $M_{24}$  is bypassed by the cascode current source formed by  $M_{b2}$  and  $M_{25}$ , easing the sizing of  $M_{24}$  to obtain large active resistance 1/  $G_{\rm ma2}$  and minimising the parasitic  $C_{\rm pa}$ .  $M_{26}$  serves as  $G_{\rm mf}$  while the output stage  $G_{\rm mL}$  is realised by  $M_{27}$ .

Experimental results: The amplifier was fabricated in 0.18 μm CMOS (Fig. 4a). At the typical  $C_{\rm L}=1$  nF, the amplifier shows a 1.13 MHz UGF at 56.2° PM. When  $C_{\rm L}$  is reduced to 0.15 nF, both UGF and PM are increased to 1.6 MHz and 76.7°, respectively. When  $C_{\rm L}$  is enlarged to 1.5 nF, the UGF is still 0.89 MHz with PM = 50°. Within  $C_{\rm L}=0.15-1.5$  nF, the average SR reduces from 0.76 to 0.28 V/μs, while the 1% settling time is increased from 2.12 to 5.35 μs (Fig. 4b). Table 1 gives the chip summary and benchmarks it with a recent work [3]. This work shows comparable UGF and SR while succeeding in reducing the die area.

Table 1: Performance summary and comparison

|                                                               | [3] ISSCC'14 | This work   |        |        |

|---------------------------------------------------------------|--------------|-------------|--------|--------|

| Load C <sub>L</sub> , nF                                      | 0.5          | 0.15        | 1      | 1.5    |

| UGF, MHz                                                      | 1.34         | 1.60        | 1.13   | 0.89   |

| Phase margin, deg                                             | 52.7         | 76.7        | 56.2   | 50.0   |

| Gain margin, dB                                               | N/A          | 4.04        | 15.2   | 17.4   |

| Average SR, V/μs                                              | 0.62         | 0.76        | 0.41   | 0.28   |

| Average $T_S$ , $\mu s$                                       | 0.62         | 2.16        | 3.87   | 5.34   |

| DC gain, dB (extrapolated)                                    | >100         | > 100       |        |        |

| Power, μW at V <sub>DD</sub> , V                              | 6.3 at 0.9   | 15.8 at 1.2 |        |        |

| Total capacitance $C_t$ and resistance $R_t$ , pF, M $\Omega$ | 0.87, 0.253  | 1, 0.125    |        |        |

| Chip area, mm <sup>2</sup>                                    | 0.007        | 0.0045      |        |        |

| CMOS technology, µm                                           | 0.18         | 0.18        |        |        |

| FOM <sub>S</sub> [(MHz·pF)/(μW·mm <sup>2</sup> )]             | 15 193       | 3376        | 15 893 | 18 776 |

| FOM <sub>L</sub> [(V/μs·pF)/(μW·mm <sup>2</sup> )]            | 7029         | 1603        | 5767   | 5907   |

| IFOM <sub>S</sub> [(MHz·pF)/(μA·mm <sup>2</sup> )]            | 13 673       | 4051        | 19 702 | 22 532 |

| IFOM <sub>L</sub> [(V/μs·pF)/(μA·mm <sup>2</sup> )]           | 6327         | 1924        | 6920   | 7089   |

Note:  $FOM_S = (UGF \cdot C_L)/(power \cdot area)$ ;  $FOM_L = (SR \cdot C_L)/(power \cdot area)$ ;  $IFOM_S = (UGF \cdot C_L)/(static \ current \cdot area)$ ;  $IFOM_L = (SR \cdot C_L)/(static \ current \cdot area)$ .

Conclusion: This Letter has proposed ECMC, APC and multi-path  $G_{\rm m}$ -boosting techniques to realise a novel ultra-compact  $10 \times$ -wide nF- $C_{\rm L}$  three-stage amplifier suitable for flat-panel-display applications. ECMC applied to the dominant compensation path saves substantial power and area, while securing a large GBW. The LHP zero also benefits the PM. For the APC, it benefits from the Miller effect to avoid the area-consuming resistor, and reduces the entailed capacitances without lowering the parasitic pole position.

Acknowledgments: This work was supported by the Macau Science and Technology Development Fund (FDCT) – 015/2012/A1 and SKL funds.

© The Institution of Engineering and Technology 2015

15 December 2014

doi: 10.1049/el.2014.4391

One or more of the Figures in this Letter are available in colour online.

Zushu Yan, Pui-In Mak, Man-Kay Law and Rui Paulo Martins (State-Key Laboratory of Analog and Mixed-Signal VLSI, and Faculty of Science and Technology – ECE, University of Macau, Macao, People's Republic of China)

⋈ E-mail: pimak@umac.mo

Rui Paulo Martins: also with Instituto Superior Técnico (IST), University of Lisbon, Portugal

## References

- 1 Huang, W.-J., Nagayasu, S., and Liu, S.-I.: 'Arail-to-rail class-B buffer with DC level-shifting current mirror and distributed Miller compensation for LCD column drivers', *IEEE Trans. Circuits Syst. I*, 2011, 58, (8), pp. 1761–1772

- 2 Yan, Z., Mak, P.-I., Law, M.-K., and Martins, R.P.: 'A 0.016-mm<sup>2</sup> 144-μW three-stage amplifier capable of driving 1-to-15 nF capacitive load with >0.95-MHz GBW', *IEEE J. Solid-State Circuits*, 2013, 48, (2), pp. 527–540

- 3 Qu, W., Im, J.-P., Kim, H.-S., and Cho, G.-H.: 'A 0.9 V 6.3 μW multistage amplifier driving 500 pF capacitive load with 1.34 MHz GBW'. IEEE ISSCC Dig. Tech. Papers, February 2014, pp. 290–291