# A 0.35-V 520-μW 2.4-GHz Current-Bleeding Mixer With Inductive-Gate and Forward-Body Bias, Achieving >13-dB Conversion Gain and >55-dB Port-to-Port Isolation

Gim Heng Tan, Harikrishnan Ramiah, Senior Member, IEEE, Pui-In Mak, Senior Member, IEEE, and Rui P. Martins, Fellow, IEEE

Abstract—An ultralow voltage micropower 2.4-GHz current-bleeding active mixer for energy-harvesting Bluetooth low energy/ZigBee applications is reported. It features a double-balanced mixer topology combining nMOS current-bleeding transistors with a pMOS local oscillator switching quad, and forward-body bias and inductive-gate bias techniques to secure an adequate performance at a supply voltage down to 0.35 V. Fabricated in 0.13- $\mu$ m CMOS, the prototype exhibits a conversion gain of 13.77 dB, a third-order intercept point of -3.5 dBm, and a noise figure of 18 dB. The power consumption is 520  $\mu$ W, and port-to-port isolation is >55 dB. The achieved figure of merit compares favorably with the state of the art.

Index Terms—Active mixer, Bluetooth low energy (BLE), CMOS, conversion gain (CG), current bleeding, energy harvesting, forward-body bias, inductive-gate bias, micropower, ultralow voltage (ULV), ZigBee.

# I. INTRODUCTION

LTRALOW power radios are on great demand for emerging highly autonomous Internet-of-Things (IoT) products conforming with the Bluetooth low energy (BLE) and ZigBee standards [1]–[3]. To enhance the power efficiency and ease the interface with the sub-0.5 V energy-harvesting sources, it is desirable to develop such radios for ultralow voltage (ULV) supplies [4], [5]. Ultralow power ULV RF circuits are especially challenging, and recent works on active mixers have saturated around 0.8 V and 1 mW [6]–[11].

Manuscript received April 28, 2016; revised September 15, 2016; accepted November 20, 2016. Date of publication December 29, 2016; date of current version April 3, 2017. This work was supported in part by the University of Malaya High Impact Research under Grant UM.C/HIR/MOHE/ENG/51, in part by the Macau FDCT SKL Fund, and in part by the University of Macau under Grant MYRG2015-00040-FST.

- G. H. Tan is with the Faculty of Engineering and Technology Infrastructure, Department of Electrical and Electronic Engineering, Infrastructure University Kuala Lumpur, 43000 Kajang, Malaysia (e-mail: ghtan@iukl.edu.my).

- H. Ramiah is with the Faculty of Engineering, Department of Electrical Engineering, University of Malaya, 50603 Kuala Lumpur, Malaysia (e-mail: hrkhari@um.edu.my).

- P.-I. Mak is with the Faculty of Science and Technology–Electrical and Computer Engineering and the State-Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macau, China (e-mail: pimak@umac.mo).

- R. P. Martins is with the State-Key Laboratory of Analog and Mixed-Signal VLSI and Faculty of Science and Technology-Electrical and Computer Engineering, University of Macau, Macau, China, and also with the Instituto Superior Técnico, Universidade de Lisboa, 1649-004 Lisbon, Portugal (e-mail: rmartins@umac.mo).

Digital Object Identifier 10.1109/TMTT.2016.2636143

In fact, ULV RF circuits normally suffer from deteriorated RF performances because of the limited transistor overdrive voltages and signal swing, and the increment of intrinsic parasitic capacitances due to larger device sizes. As a result, a higher bias current is expected for ULV RF circuits to preserve or recover dynamic performances, being a hard tradeoff with the power consumption.

Typical down-conversion active mixers offer balanced RF performances in terms of conversion gain (CG), noise figure (NF), and linearity [12]. This architecture stacks an RF transconductance stage, a LO switching quad and a load resistors atop of each other under the supply rail. Hence, active mixers can normally operate at a high supply voltage, being impracticable for ULV implementation. The invention of the folded active mixer has reduced the number of transistors stacked below the supply rail, by folding out the LO switching quad and IF output from the RF transconductance stage [13], [14]. However, extra power is consumed as the bias current for the transconductance stage and LO switching quad is only partially shared [5]. Current-bleeding active mixer is an alternative as it can significantly boost the CG and NF [14], [15]. In this topology, the bias current through the RF transconductance stage is the sum of those from the LO switching stage and current-bleeding stage. Less current flows through the LO switching transistors result in smaller device sizes, as well as gate-source capacitances. Then, substantial improvement of the switching efficiency has been possible [16].

For CMOS circuits' design at typical supply voltages, the junction between the body and source of the transistor is zero- or reverse-biased to minimize the body leakage current flow into the substrate. Alternatively, for ULV operation, the body-to-source terminal can be forward-biased properly to reduce the transistor's threshold voltage  $V_{\rm th}$  [17], [18]. As the body-to-source voltage is lower than the p-n junction turn-ON voltage under a ULV supply, the induced body-leakage current is negligible. With the reduced  $V_{\rm th}$ , a ULV mixer with adequate performances becomes more promising even with transistor stacking [19].

Herein, we propose a ULV double-balanced active mixer. It innovates by associating inductive-gate bias and forward-body bias techniques, together with a combination of an nMOS current-bleeding transistor and a pMOS local oscillator (LO)

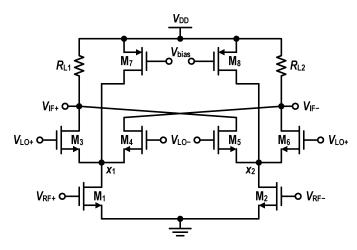

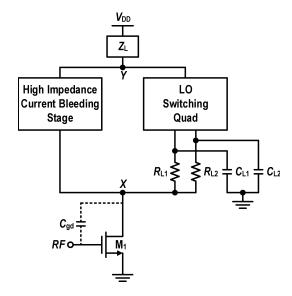

Fig. 1. Conventional current-bleeding double-balanced active mixer.

switching quad, to achieve 0.35-V operation at 2.4 GHz. With such a topology, the required voltage to bias the gate of the LO switching quad is no longer dependent on the RF transconductance stage. The nMOS current-bleeding transistors offer additional shielding between the LO and RF ports, improving their isolation significantly even at ULV. The CG is also improved without extra power consumption due to the inductive-gate bias on the current-bleeding transistors to boost up the transconductance current. To the best of our knowledge, it is the first CMOS active mixer operating down to a 0.35V supply, while measuring a CG of >13 dB and a port-to-port isolation of >55 dB.

This paper is organized as follows. Section II addresses the ULV mixer circuit design and analysis. Section III reports the simulation and experimental results, and the conclusion is drawn in Section IV.

## II. ULV MIXER DESIGN AND ANALYSIS

A typical double-balanced active mixer with current bleeding is shown in Fig. 1. The LO switching quad  $(M_3-M_6)$  is stacked atop the RF transconductance stage  $(M_1$  and  $M_2)$  [20] for RF-to-IF down-conversion. To enhance the switching efficiency of  $M_3-M_6$ , pMOS current-bleeding transistors  $(M_7-M_8)$  are added to assign more bias current to  $M_1-M_2$ . The gate-bias voltage of  $M_3-M_6$  can be made slightly above  $V_{\rm th}$ , as minimally given by

$$V_{\rm LO} = V_{\rm gs3} + V_{\rm ds1(sat)} \tag{1}$$

where  $V_{\rm gs3}$  is the gate-to-source voltage of  $M_3$  and  $V_{\rm dsl(sat)}$  is the drain-to-source overdrive voltage of  $M_1$ . From (1), the high dc voltage required to switch ON  $M_3$ – $M_6$  outlays the limitation of it in ULV operation.

## A. pMOS-Based LO Switching Quad With Low DC Bias

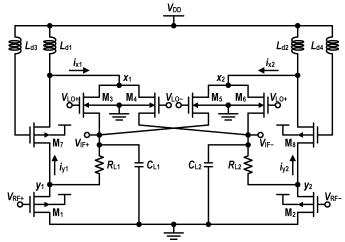

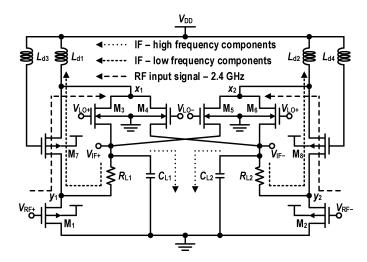

Fig. 2 shows the proposed ULV active mixer encapsulating an RF transconductance stage  $(M_1-M_2)$ , a pMOS LO switching quad  $(M_3-M_6)$ , an nMOS current-bleeding stage  $(M_7-M_8)$ , and an RC load  $(R_{L1}, C_{L1})$  and  $(R_{L2}, C_{L2})$ .

Fig. 2. Proposed ULV double-balanced active mixer with high RF-LO isolation.

TABLE I

CIRCUIT PARAMETERS OF THE ULV ACTIVE MIXER

| PARAMETERS                        | Design Values |

|-----------------------------------|---------------|

| M <sub>1</sub> , M <sub>2</sub>   | 116 / 0.13 μm |

| M <sub>3</sub> –M <sub>6</sub>    | 64 / 0.13 µm  |

| $M_7$ , $M_8$                     | 250 / 0.13 μm |

| $L_{ m d1},L_{ m d2}$             | 6.7 nH        |

| $L_{\mathrm{d3}},L_{\mathrm{d4}}$ | 6.7 nH        |

| $C_{L1}, C_{L2}$                  | 10 pF         |

| RL1, RL2                          | 1 kΩ          |

Inductors  $L_{\rm d1}$  and  $L_{\rm d2}$  operate as RF chokes in alleviating the RF signal from leaking into the voltage supply  $(V_{\rm DD})$ . Inductors  $L_{\rm d3}$  and  $L_{\rm d4}$  are added to the gates of  $M_7$  and  $M_8$  to enhance the CG (details later). The RF signal is mixed with LO at nodes  $x_1$  and  $x_2$ , between the inductors  $L_{\rm d1}$  and  $L_{\rm d2}$  and the LO switching quad. Transistors  $M_1$  and  $M_7$  are designed in cascoded configuration to increase the impedance seen into node  $x_1$ , improving the LO-RF isolation. Differing from the typical active mixers, the bodies of the nMOS and pMOS devices are connected to  $V_{\rm DD}$  and ground, respectively, in order to forward-bias their body-to-source terminals. For an n-channel MOS, its  $V_{\rm th}$  is given by [17]

$$V_{\rm th} = V_{\rm th0} + \gamma \left( \sqrt{2\Phi_f - V_{\rm bs}} \right) - \sqrt{2\Phi_f} \tag{2}$$

where  $V_{\text{th0}}$  is the threshold voltage when  $V_{\text{bs}} = 0$ ,  $\gamma$  is the body-effect coefficient,  $\Phi_f$  is the bulk Fermi potential, and  $V_{\text{bs}}$  is the voltage between the body and source. Table I summarizes the circuit parameters of the mixer.

By raising the dc voltage at the body terminal properly, the value of  $V_{\rm bs}$  becomes positive lowering the effective  $V_{\rm th}$ . Also, the effective  $V_{\rm th}$  can be controlled by the bias voltage of the body, which allows dynamic control of  $V_{\rm th}$  for ULV operation. With the reduced  $V_{\rm th}$ , the minimum  $V_{\rm DD}$  to operate the mixer can be reduced significantly, even with transistor stacking. Although  $V_{\rm bs}$  is forward-biased, it is still well below the

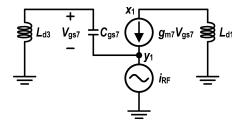

Fig. 3. Small-signal analysis of the proposed ULV active mixer.

turn-ON voltage of the p-n junction, which is  $\sim 0.7$  V. Thus, the induced body leakage current is negligible. Recalling that the typical active mixer (Fig. 1) requires a dc voltage headroom of >0.5 V to bias the gate of the nMOS LO switching quad, the minimum dc voltage here is reduced substantially. As a result, the high-voltage constraint of typical active mixers is resolved by reducing the input dc voltage entailed to bias the gate of the LO transistors. Also, using pMOS as the LO switching quad  $(M_3-M_6)$  coupled with the inductors, as illustrated in Fig. 2, the term  $V_{ds1(sat)}$  in (1) can be eliminated. Also, the bias voltage required to turn ON the LO switching quad no longer depends on  $V_{ds1(sat)}$  of  $M_1$  and  $M_2$ , which renders this design friendly for ULV operation. The dc voltage required to bias the gate of  $M_3$ - $M_6$  is reduced to  $V_{\rm sg}$  (source-to-gate voltage) that is almost identical to  $V_{th}$  of the pMOS transistor. The dc voltage at nodes  $x_1$  and  $x_2$  is approximately  $V_{DD}$  with  $V_{\rm sg3} = V_{\rm th}$ -the bias voltage, and thus  $V_{\rm LO}$  is given by

$$V_{\rm LO} = V_{\rm DD} - V_{\rm th}. \tag{3}$$

Hence,  $V_{\rm DD}$  can be as low as  $\sim 0.35$  V for  $V_{\rm th} = \sim 250$  mV. A dc voltage of 100 mV is adequate to bias the gate of  $M_3$ – $M_6$ . The proposed mixer is designed with an optimum CG at LO power of 0 dBm. The peak amplitude of 316 mV that corresponds to 0 dBm from the LO port is converted differentially to a peak amplitude of 158 mV with a dc offset of 100 mV to drive the input of the differential mixer. Comparatively, for the typical current-bleeding active mixer, such a bias voltage, should be as high as  $V_{\rm DD}$ .

## B. Current-Bleeding Transistors With Inductive-Gate Bias

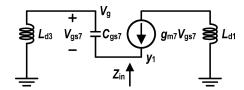

Inductors  $L_{\rm d3}$  and  $L_{\rm d4}$  added to the gate of  $M_7$  and  $M_8$  can effectively enhance the CG. To exemplify it, a small-signal equivalent model of  $M_7$  with  $L_{\rm d3}$  is built as shown in Fig. 3.  $L_{\rm d3}$  at the gate of  $M_7$  enhances the small-signal amplitude of the gate-to-source voltage  $V_{\rm gs7}$ , which subsequently boosts the effective small-signal RF transconductance current, before mixing with the LO signal at node  $x_1$ . The small-signal current entering node  $y_1$  is given by

$$i_{y1} = g_{m1} \cdot \frac{V_{RF}}{2} \cdot \sin\left(\omega_{RF}t\right) \tag{4}$$

where  $g_{m1}$  is the transconductance of  $M_1$  and  $\omega_{RF}$  is the RF angular frequency. As  $L_{d3}$  (6.7 nH) and  $M_7$  (250/0.13  $\mu$ m) are relatively large, the impedance seen into the source of  $M_7$  is approximately  $1/g_{m7}$ . Thus, the small-signal voltage looking into the source of  $M_7$  is given by

$$V_{\rm y1} = \frac{g_{\rm m1}}{g_{\rm m7}} \cdot \frac{V_{\rm RF}}{2} \cdot \sin\left(\omega_{\rm RF}t\right). \tag{5}$$

By ignoring the gate-to-drain capacitance  $C_{\rm gd7}$  of  $M_7$ , its  $V_{\rm gs7}$  can be expressed by

$$V_{gs7} = \frac{-\left(\frac{1}{j\omega_{RF} \cdot C_{gs7}} \cdot V_{y1}\right)}{\frac{1}{j\omega_{RF} \cdot C_{gs7}} + j\omega_{RF} \cdot L_{d3}}.$$

(6)

Substituting  $V_{v1}$ , we get

$$V_{gs7} = \frac{-\frac{g_{m1}}{g_{m7}} \cdot \frac{V_{RF}}{2} \cdot \sin(\omega_{RF}t)}{\left(1 - \omega_{RF}^2 \cdot L_{d3} \cdot C_{gs7}\right)}.$$

(7)

From (7), it is clear that if  $(1 - \omega_{RF}^2 \cdot L_{d3} \cdot C_{gs7}) < 1$ ,  $V_{gs7}$  can be boosted by  $L_{d3}$ . with no extra power consumption. The small-signal RF current  $i_{x1}$  at node  $x_1$  is given by

$$i_{x1} = \frac{-g_{m7} \cdot \left(\frac{1}{j\omega_{RF} \cdot C_{gs7}}\right) \cdot \frac{g_{m1}}{g_{m7}} \cdot \frac{V_{RF}}{2} \cdot \sin(\omega_{RF}t)}{\frac{1}{j\omega_{RF} \cdot C_{gs7}} + j\omega_{RF} \cdot L_{d3} \cdot C_{gs7}}$$

$$= \frac{-g_{m1} \cdot \frac{V_{RF}}{2} \cdot \sin(\omega_{RF}t)}{1 - \omega_{RF}^{2} \cdot L_{d3} \cdot C_{gs7}}.$$

(8)

Similarly, the out-phased small-signal current at node  $x_2$  is

$$i_{x2} = \frac{g_{\text{m1}} \cdot \frac{V_{\text{RF}}}{2} \cdot \sin\left(\omega_{\text{RF}}t\right)}{1 - \omega_{\text{RF}}^2 \cdot L_{\text{d3}} \cdot C_{\text{gs7}}}.$$

(9)

Thus, the differential mixer output current is derived as

$$i_{\rm IF} = (i_{x1} - i_{x2}) \cdot \operatorname{sq}(\omega_{\rm LO}t) \tag{10}$$

where  $sq(\omega_{LO}t)$  is the square-wave input for LO hard switching, which can be described as [21]

$$\operatorname{sq}(\omega_{\mathrm{LO}}t) = \frac{4}{\pi} \left( \sin \omega_{\mathrm{LO}}t + \frac{1}{3} \sin 3\omega_{\mathrm{LO}}t + \frac{1}{5} \sin 5\omega_{\mathrm{LO}}t + \cdots \right). \tag{11}$$

By considering only the desired frequency spectrum for down-conversion and neglecting the higher order terms as these spurs are filtered out at the subsequent stage of a receiver, the  $i_{\rm IF}$  can be expressed as

$$i_{\text{IF}} = \frac{2g_{\text{m(1,2)}} \cdot V_{\text{RF}}}{\pi \left(1 - \omega_{\text{RF}}^2 \cdot L_{\text{d3}} \cdot C_{\text{gs7}}\right)} \cdot \left(\sin\left(\omega_{\text{RF}} - \omega_{\text{LO}}\right)t - \sin\left(\omega_{\text{RF}} + \omega_{\text{LO}}\right)\right). \quad (12)$$

Finally, we deduce the CG as given by

$$\frac{V_{\rm IF}}{V_{\rm RF}} = \left(\frac{2g_{m(1,2)}}{\pi \left(1 - \omega_{\rm RF}^2 \cdot L_{\rm d3} \cdot C_{\rm gs7}\right)}\right) \cdot R_{\rm L(1,2)} \cdot \sin\left(\omega_{\rm RF} - \omega_{\rm LO}\right) t. \tag{13}$$

From (13), it can be deducted that the mixer's CG is improvable under  $(1 - \omega_{RF}^2 \cdot L_{d3} \cdot C_{gs7}) < 1$ . At 2.4 GHz,  $L_{d3} = 6.7$  nH and  $C_{gs7} \approx 300$  fF were chosen to achieve

$$(1-\omega_{RF}^2 \cdot L_{d3} \cdot C_{gs7}) = 1 - (2\pi \times 2.4G)^2 \times 6.7n \times 300f \approx 0.54.$$

Consequently, the overall CG is derived as

$$\frac{V_{\rm IF}}{V_{\rm RF}} = \left(\frac{2g_{m(1,2)}}{\pi \times 0.54}\right) \cdot R_{L(1,2)} \cdot \sin(\omega_{\rm RF} - \omega_{\rm LO})t \tag{14}$$

which shows that the CG is increased by a value higher than two.

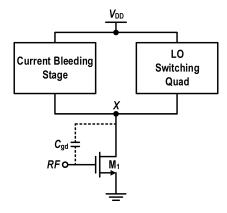

Fig. 4. LO leakage for a current-bleeding active mixer (single-ended).

## C. Improved LO-to-RF Isolation at ULV Headroom

High isolation between the LO and RF ports is crucial for direct-conversion receivers as the time-varying dc offset can highly degrade the signal quality [22], [23]. Here, the term isolation is defined as the difference in power between the input signal and the corresponding leakage component of the input power at the respective ports. Any device mismatches in the LO switching quad will potentially couple the LO leakage to the RF port, via the gate-drain capacitance,  $C_{gd}$ , of the RF transconductance transistors. The typical LO-to-RF isolation of an active mixer is 40-50 dB [24]. The common approach to improve the isolation is to add another transistor between the RF transconductance stage and the LO switching stage, providing additional shielding from the LO-leakage components [25], [26]. Yet, this solution entails extra voltage headroom, which is not feasible here in the ULV design. Given that our mixer integrates an nMOS current-bleeding transistor, the isolation between the LO and RF ports can benefit from it. Fig. 4 shows a simplified view of the singleended current-bleeding mixer that integrates a combination of a pMOS current-bleeding stage and an nMOS LO switching quad. If the differential devices of the LO switching quad are not perfectly matched, the first harmonic of the LO signal at node X cannot be fully canceled, generating an LO leakage at the RF port [27]. Such a leakage will be coupled to the RF port through the intrinsic  $C_{\rm gd}$  of the transconductance stage  $M_1$ . In fact, to achieve high linearity, larger values of the dc current and  $g_{\rm m}$  of  $M_1$  are required, which results in a larger transistor sizing. The latter proportionally increases the intrinsic  $C_{\rm gd}$ , degrading the LO-RF isolation.

Fig. 5 shows the conceptual block diagram of the proposed mixer where the RF port has been shielded from the LO leakage path by the high-impedance current-bleeding stage.  $Z_{\rm L}$  defines the RF choke. LO leakage potentially couples through node X or Y to the RF port. The advantage of the proposed mixer is that the current-bleeding stage and  $M_1$  are cascoded, which implies a high impedance referring into the node Y, thus, subsequently preventing the LO leakage from coupling to the RF port.

The observed high impedance  $R_x$  referring into the drain terminal of the bleeding transistor  $M_7$  of Fig. 2 is expressed as

$$R_x \approx g_{\rm m7} \cdot r_{\rm o1} \cdot r_{\rm o7} \tag{15}$$

Fig. 5. High LO-RF isolation of the proposed ULV active mixer.

Fig. 6. Impedance looking into the nMOS bleeding transistor.

where  $g_{m7}$  is the transconductance of  $M_7$  and  $r_{o1}(r_{o7})$  is the output resistance of  $M_1(M_7)$ . Comparatively, the LO leakage components at nodes  $x_1$  and  $x_2$ , as shown in Fig. 4, will directly couple to the RF port through  $C_{\rm gd}$  without any extra shielding between the LO-RF port. The proposed mixer benefits from the high input impedance of the current-bleeding transistor as an additional shielding element between the LO and RF ports for better LO-RF isolation.

# D. Stability of the Mixer

The stability concern arises due to the integration of the inductors  $L_{\rm d(3,4)}$  at the gate of the bleeding transistors. Such inductors potentially cause negative impedance ( $Z_{\rm in}$ ) referring into the source terminal of the bleeding transistor. A well-designed circuit is essential for this mixer, and insight of the small-signal analysis has to be undertaken to ensure that the circuit is able to operate properly without instability. Fig. 6 shows the small-signal model for the analysis of  $Z_{\rm in}$

$$Z_{\rm in} = \left(\frac{1}{g_{m7} + j\omega_{\rm RF} \cdot C_{\rm gs7}}\right) \cdot \left(1 - \omega_{\rm RF}^2 \cdot L_{\rm d3} \cdot C_{\rm gs7}\right). \quad (16)$$

From (16),  $(1 - \omega_{RF}^2 \cdot L_{d3} \cdot C_{gs7}) > 0$  and this proves that the mixer is in stable condition at 2.4 GHz.

# E. Leakage of Spurious Signals at the IF Output

Fig. 7 illustrates the various feedthrough paths for the IF signals, which potentially leak to other nodes of the circuit. The spurious signals located at the output IF port

Fig. 7. Analysis of output spurs.

might leak through resistors  $R_{L(1,2)}$ . High-frequency spurious would initially short to ground through capacitor  $C_{L(1,2)}$ . Thus, only the IF signal and other low-frequency spurious leak through resistors  $R_{L(1,2)}$ . At nodes  $x_1$  and  $x_2$ , the low-frequency components together with the RF input signal will flow through  $M_{3,4}$  and reach the nodes  $y_1$  and  $y_2$ .

$L_{d(1,2)}$  resonates with the parasitic capacitance to present a high impedance path at the operating frequency to prevent RF signal leakage through  $V_{\rm DD}$ , eventually driving the majority of the RF signal toward the LO switching quad. The low-frequency components that are far away from the resonant frequency will sink to  $V_{\rm DD}$  through inductors  $L_{d(1,2)}$ , instead of flowing into the LO switching quad.

# F. Noise and Linearity Analysis of the Mixer

The noise of the proposed mixer is analysed based on the thermal noise contributed by load resistor, LO switches, RF transconductance stage, and cascoded transistor. The total output noise is given as [28]

$$\overline{(V_{n,\text{out}}^{2})} = 8KTR_{L(1,2)} + 16KT\gamma \left[ \frac{R_{L(1,2)}^{2}I}{\pi A} \right] + \frac{8KT\gamma}{g_{\text{m}(1,2)}} \left( \left| \frac{V_{\text{IF}}}{V_{\text{RF}}} \right| \right)^{2} + 8KT\gamma g_{\text{m}(7,8)} \left[ \frac{2R_{L(1,2)}}{\pi} + \frac{1}{g_{\text{m}(7,8)}} \left( \left| \frac{V_{\text{IF}}}{V_{\text{RF}}} \right| \right)^{2} \right] \tag{17}$$

where K is Boltzmann's constant, T is the absolute temperature, and  $\gamma$  is the channel noise factor, conventionally given as 2/3 for long channel transistors, but can be higher for short channel devices, A is the LO amplitude, and I is the mixer dc bias current. The first term is due to the two load resistors,  $R_{L(1,2)}$ , the second term is the output noise due to the four switches  $(M_3-M_6)$ , the third term shows the noise of the RF transconductance stage  $(M_1$  and  $M_2)$  transferred to the mixer output, and the fourth term is the output noise due to the cascoded transistor  $M_7$  and  $M_8$ . As it is observed from (17), the output noise increases with the integration of the cascoded transistor.

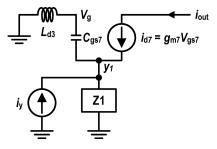

Fig. 8. Equivalent-circuit model for Volterra series analysis.

In computing the linearity performance of the proposed architecture, the small-signal equivalent model of the cascode amplifier transistor in Fig. 8 is adopted to derive the first- and third-order coefficients of the Volterra series using harmonic input method. The common-source transistor is modeled by a Norton equivalent circuit with a current source  $i_y$  and a transformed output impedance of  $Z_1$  [29]. Using Volterra series [30], the third-order intercept amplitude,  $AIP_3$  of the proposed architecture can be derived to be

$$AIP_{3}^{2}(2\omega_{b} - \omega_{a}) = \frac{4}{3}g_{m7,1} \cdot \frac{1}{[1 + g_{m7,1}A_{1}(j\omega)] \cdot |A_{1}(j\omega)|^{2}} \cdot \frac{1}{\varepsilon(\Delta\omega, 2\omega)}$$

(18)

where

$$g(\omega) = j\omega C_{gs7} + Y_1(j\omega) \cdot \left[1 - \omega^2 C_{gs7} L_{d3}\right]$$

(19)

$$\varepsilon(\Delta\omega, 2\omega) = \frac{2}{3} g_{m7,2}^2 \cdot \left[\frac{2}{g_{m7,1} + g(\Delta\omega)} + \frac{1}{g_{m7,1} + g(2\omega)}\right]$$

+  $g_{m7,3}$  (20)

given that

$$g_{\text{m7,1}} = g_{\text{m7}}$$

$$g_{\text{m7,2}} = \frac{g'_{\text{m7}}}{2!}$$

$$g_{m7,3} = \frac{g''_{\text{m7}}}{3!}$$

(21)

and

$$A_1(j\omega) = -\frac{1}{g_{\text{m7,1}} + sC_{\text{gs7}} + \frac{1}{Z_1(j\omega)} \cdot \left[1 + s^2C_{\text{gs7}}L_{\text{d3}}\right]}.$$

(22)

In order to improve the linearity, the resulting  $AIP_3$  needs to be increased. In the definition of  $(1 - \omega^2 \cdot C_{gs7} \cdot L_{d3}) \approx 0.54$  with the inductor being integrated, the linearity is enhanced as the component  $\varepsilon(\Delta\omega, 2\omega)$  is reduced.

## III. SIMULATED AND EXPERIMENTAL RESULTS

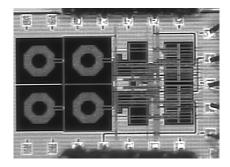

The proposed ULV mixer was fabricated in a standard 0.13- $\mu$ m triple-well CMOS technology. Fig. 9 shows the chip micrograph that includes the mixer and its test buffer. The die area is 0.84  $\times$  1.23 mm<sup>2</sup>.

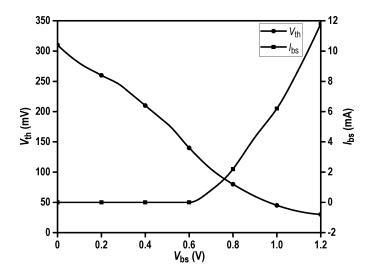

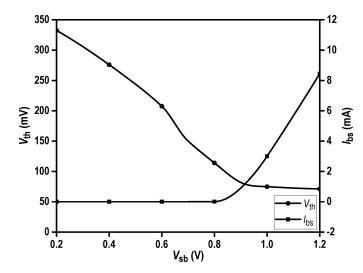

Fig. 10 illustrates the simulated bulk current and threshold voltage changes against  $V_{\rm bs}$  of the nMOS transistor. At a 0.35 V  $V_{\rm DD}$ , the leakage current at the substrate is almost

Fig. 9. Chip photograph of the fabricated active mixer.

Fig. 10.  $V_{\text{th}}$  and  $I_{\text{bs}}$  versus  $V_{\text{bs}}$  voltage simulated for nMOS.

Fig. 11.  $V_{\text{th}}$  and  $I_{\text{bs}}$  versus  $V_{\text{bs}}$  voltage simulated for pMOS.

negligible, and  $V_{\rm th}$  has been reduced to  $\sim\!220$  mV, which is beneficial for a ULV design. It is apparent that  $V_{\rm bs}$  must be <0.7 V. Similar results for the pMOS transistor are given in Fig. 11. At  $V_{\rm bs}=0.35$  V,  $V_{\rm th}$  is  $\sim\!300$  mV and  $V_{\rm bs}$  must be <0.8 V.

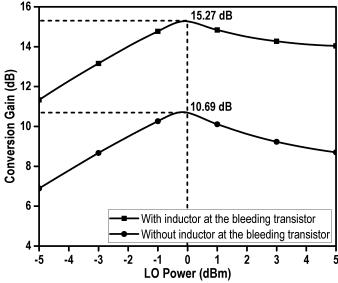

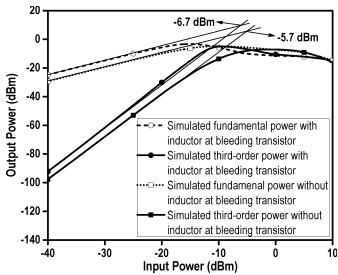

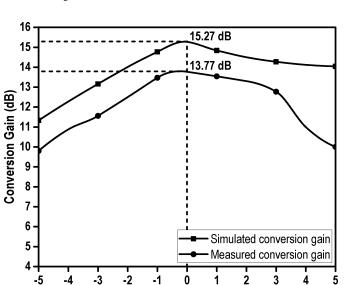

Fig. 12 exhibits the CG with the presence of  $L_{d3}$  and  $L_{d4}$ . The simulated CG shows an increment of 4.58 dB at the

Fig. 12. Simulated CG versus LO power with and without inductor at the bleeding transistor.

Fig. 13. Simulated  $IIP_3$  versus RF input power with and without inductor at the bleeding transistor.

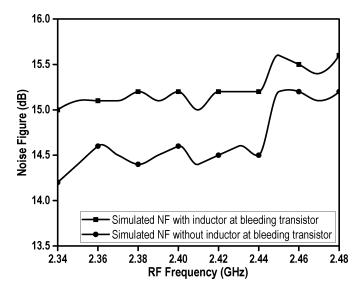

optimum LO power of 0 dBm. As the parasitic capacitor at the source of the LO switching quad has been resonated out by  $L_{d1}$  and  $L_{d2}$ , the small-signal RF current leakage into the parasitic capacitor [31], [32] at the resonant frequency of 2.4 GHz is reduced as well, benefiting further the CG. Figs. 13 and 14 show the graph for the simulated linearity and NF, respectively, with and without the integration of  $L_{d3}$  and  $L_{d4}$ . Without the inductor in place, a CG of 10.69 dB and a linearity of about -5.7 dBm are observed. With the inductor integrated, the CG increases to 15.27 dB with a linearity at about -6.7 dBm. The plot of NF with the inductor in place in Fig. 14 shows a slight increase in the value of NF due to the integration of a low-Q on-chip inductor.

Fig. 15 shows the simulated and measured CG of the mixer with the corresponding LO power. With a fixed RF power

Fig. 14. Simulated NF versus RF input frequency with and without inductor at the bleeding transistor.

Fig. 15. Simulated and measured CG.

at 2.4 GHz while sweeping the LO power, the CG of the mixer can be calculated as

LO Power (dBm)

$$CG (dB) = P_{IF} - P_{RF}$$

(23)

where  $P_{\rm IF}$  is the output power obtained from the spectrum analyzer and  $P_{\rm RF}$  is the input RF power applied from the signal generator. The optimum CG is  $\sim 13.77$  dB at LO power = 0 dBm. The discrepancy between the simulated and measured CG is  $\sim 1.5$  dB, which is likely due to the coupling effect of process variation in the fabrication.

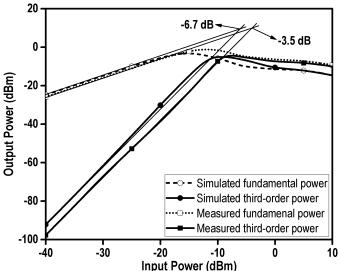

The linearity performance is measured via a two-tone test at 2.443 and 2.4442 GHz, along with an LO input at 0 dBm. The input-referred third-order intercept point (IIP<sub>3</sub>) is -6.7 dBm from simulation and -3.5 dBm from measurement, as shown in Fig. 16.

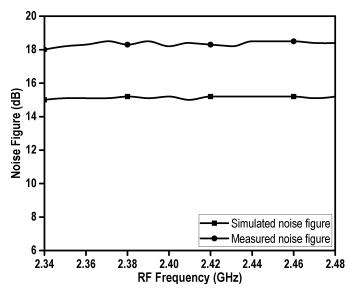

The measured NF is  $\sim$ 18 dB as shown in Fig. 17. Note that this NF is acceptable, as its noise contribution is reduced

Fig. 16. Simulated and measured IIP3.

Fig. 17. Simulated and measured NF.

by the gain of its forefront LNA in a receiver. Nevertheless, the NF is not a very critical parameter for ZigBee applications [33]. The simulated and measured NF varies around ~3 dB; this difference is largely due to the lower CG that contributes to the increased NF. The parasitic capacitance at the common-source node of the switching stage degrades the NF of the mixer. The architecture in [20] integrates the inductors to improve the NF by tuning out the parasitic capacitances at the source node of the LO switching transistor. However, these inductors are not fully utilized to reduce the total dc voltage headroom as they are in parallel with the source of the LO switching node. In the proposed design, inductor  $L_{d(1,2)}$  is in series with the mixer core circuit, which reduces the required voltage headroom while being capitalized to resonate out the parasitic capacitance at the source node of the LO switching transistor to improve the NF. On the other hand, the impedance seen into the source of the LO switching

| Parameters             | [34]<br>MWCL'12 | [18]<br>TMTT'12 | [35]<br>TMTT'12 | [36]<br>TMTT'15 | [37]<br>MWCL'09 | [38]<br>ISCAS'14 | [39]<br>MWCL'07 | This<br>Work |

|------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|--------------|

| V <sub>DD</sub> (V)    | 1.2             | 0.8             | 0.6             | 1.2             | 1.5             | 0.8              | 0.77            | 0.35         |

| Power (mW)             | 16.8            | 0.88            | 0.6             | 5.82            | 5.3             | 9.8              | 0.48            | 0.52         |

| f <sub>RF</sub> (GHz)  | 0.87            | 0.2-13          | 8.65            | 2.4             | 2–2.7           | 8                | 0.5–7.5         | 2.4          |

| CG (dB)                | 13.5            | 9.9             | 6               | 13.61           | 13.5            | 9.4              | 5.7             | 13.74        |

| IIP <sub>3</sub> (dBm) | -13             | -10             | -8              | -4.46           | -6              | -3.8             | -5.7            | -3.5         |

| NF (dB)                | 2.7             | 11.7            | 15.9            | 20              | 8               | 20.9             | 15              | 18           |

| LO-RF Isolation (dB)   | -               | -               | 31.2            | 65.4            | -               | 60               | -               | 61           |

| CMOS Technology (µm)   | 0.13            | 0.18            | 0.13            | 0.13            | 0.13            | 0.18             | 0.18            | 0.13         |

| FOM                    | 10.29           | 13.80           | 10.32           | 1.93            | 13.50           | -3.01            | 13.2            | 14.96        |

TABLE II

PERFORMANCE SUMMARY AND COMPARISON

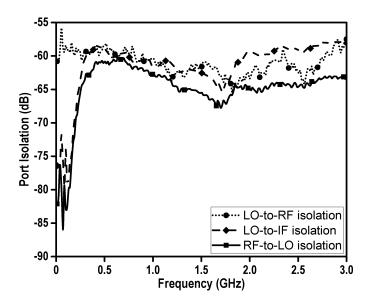

Fig. 18. Measured port-to-port isolation.

stage is purely a real impedance, and thus the parasitic capacitance at the switching node successfully resonates out with the inductor at the resonant frequency of 2.4 GHz.

Fig. 18 shows the measured port-to-port isolation between the mixer's input and output. The isolation is >55 dB between the LO, RF, and IF ports. Due to the cascode configuration of  $M_1$  and  $M_7$ , this mixer exhibits higher isolation between the LO and RF ports. At 2.4 GHz, the isolation is as high as 61 dB, which is superior at ULV.  $M_7$  and  $M_8$  also add extra shielding between the LO and RF ports, as they are added between the LO switching quad and the RF transconductance stage. The LO leakage to the output nodes  $V_{\rm IF+}$  and  $V_{\rm IF-}$  is insignificant as it will flow to the ground rail, instead of the RF port, as the capacitance  $C_{\rm L1}$  or  $C_{\rm L2}$  provides a very low impedance path to ground at 2.4 GHz. Any LO leakage at the output port will be further attenuated by the load resistor  $R_{\rm L(1,2)}$  before reaching the RF port, leading to an improvement in the LO-RF isolation.

Table II compares the implemented architecture to state-ofthe-art CMOS implementation that have already been reported in literature. The dynamic performance is evaluated using the Figure-of-Merit (FOM) from [13]

$$FOM = 10 \log \left( \frac{10^{G/20} \cdot 10^{(IIP_3 - 10)/20}}{10^{NF/10} \cdot P} \right)$$

(24)

where G is the general voltage gain (or CG) (dB), IIP<sub>3</sub> is the third order linearity (dBm), NF is given in decibels, and P is the power (mW). This paper succeeds in achieving a high FOM of 14.97, while operating at a ULV supply of 0.35 V.

## IV. CONCLUSION

This paper reported the design and implementation of a ULV 2.4-GHz current-bleeding active mixer in 0.13- $\mu m$  CMOS. It features a mixer topology combining nMOS current-bleeding transistors, a pMOS LO switching quad, and forward-body bias and inductive-gate bias techniques to enable concurrently ULV operation (0.35 V) and ultralow power consumption (520  $\mu$ W). The overall performance renders it highly suitable for ultralow power ULV energy-harvesting radios such as BLE and ZigBee for IoT applications.

#### REFERENCES

- [1] T. Song, H. S. Oh, E. Yoon, and S. Hong, "A low-power 2.4-GHz current-reused receiver front-end and frequency source for wireless sensor network," *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1012–1022, May 2007.

- [2] W.-K. Chong, H. Ramiah, G.-H. Tan, N. Vitee, and J. Kanesan, "Design of ultra-low voltage integrated CMOS based LNA and mixer for ZigBee application," *AEU-Int. J. Electron. Commun.*, vol. 68, no. 2, pp. 138–142, Feb. 2014.

- [3] K.-H. Liang and H.-Y. Chang, "0.5–6 GHz low-voltage low-power mixer using a modified cascode topology in 0.18 μm CMOS technology," *IET Microw., Antennas Propag.*, vol. 5, no. 2, pp. 167–174, Jan. 2011.

- [4] Y.-I. Kwon, S.-G. Park, T.-J. Park, K.-S. Cho, and H.-Y. Lee, "An ultralow-power CMOS transceiver using various low-power techniques for LR-WPAN applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 2, pp. 324–336, Feb. 2012.

- [5] H. H. Hsieh and L. H. Lu, "Design of ultra-low-voltage RF frontends with complementary current-reused architectures," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 7, pp. 1445–1458, Jul. 2007.

- [6] A. H. M. Shirazi and S. Mirabbasi, "An ultra-low-voltage ultra-low-power CMOS active mixer," *Analog Integr. Circuits Signal Process.*, vol. 77, no. 3, pp. 513–528, Dec. 2013.

- [7] M. Rahman and R. Harjani, "A 0.7V 194 μW 31dB FOM 2.3–2.5 GHz RF frontend for WBAN with mutual noise cancellation using passive coupling," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, May 2015, pp. 175–178.

- [8] M. A. Abdelghany, R. K. Pokharel, H. Kanaya, and K. Yoshida, "Low-voltage low-power combined LNA-single gate mixer for 5GHz wireless systems," in *Proc. IEEE Radio-Freq. Integr. Circuits Symp.*, Jun. 2011, pp. 1–4.

- [9] L. Xu, C.-H. Chang, and M. Onabajo, "A 0.77 mW 2.4 GHz RF frontend with -4.5 dBm in-band IIP3 through inherent filtering," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 5, pp. 352–354, May 2016.

- [10] J. Deguchi, D. Miyashita, and M. Hamada, "A 0.6V 380 μW –14 dBm LO-input 2.4 GHz double-balanced current-reusing single-gate CMOS mixer with cyclic passive combiner," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2009, pp. 224–225.

- [11] A. Selvakumar, M. Zargham, and A. Liscidini, "Sub-mW current reuse receiver front-end for wireless sensor network applications," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2965–2974, Dec. 2015.

- [12] P. J. Sulivan, B. A. Xavier, and W. H. Ku, "Low voltage performance of a microwave CMOS Gilbert cell mixer," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 1151–1155, Jul. 1997.

- [13] V. Vidojkovic, J. van der Tang, A. Leeuwenburgh, and A. H. M. van Roermund, "A low-voltage folded-switching mixer in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1259–1264, Jun. 2005.

- [14] M.-F. Huang, C. J. Kuo, and S.-Y. Lee, "A 5.25-GHz CMOS folded-cascode even-harmonic mixer for low-voltage applications," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 2, pp. 660–669, Feb. 2006.

- [15] H. Cruz, H.-Y. Huang, S.-Y. Lee, and C.-H. Luo, "A 1.3 mW low-IF, current-reuse, and current-bleeding RF front-end for the MICS band with sensitivity of -97 dBm," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 6, pp. 1627–1636, Jun. 2015.

- [16] G. H. Tan, R. M. Sidek, and M. M. Isa, "Design of ultra-low voltage and low-power CMOS current bleeding mixer," in *Proc. IEEE Asia–Pacific Conf. Circuits Syst.*, Nov. 2014, pp. 344–347.

- [17] D. Wu, R. Huang, W. Wong, and Y. Wang, "A 0.4-V low noise amplifier using forward body bias technology for 5 GHz application," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 7, pp. 543–545, Jul. 2007.

- [18] M. G. Kim, H. W. An, Y. M. Kang, J. Y. Lee, and T. Y. Yun, "A low-voltage, low-power, and low-noise UWB mixer using bulkinjection and switched biasing techniques," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 8, pp. 2486–2493, Aug. 2012.

- [19] C.-L. Kuo, B.-J. Huang, C.-C. Kuo, K.-Y. Lin, and H. Wang, "A 10–35 GHz low power bulk-driven mixer using 0.13 μm CMOS process," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 7, pp. 455–457, Jul. 2008.

- [20] J. Park, C.-H. Lee, B.-S. Kim, and J. Laskar, "Design and analysis of low flicker-noise CMOS mixers for direct-conversion receivers," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 12, pp. 4372–4380, Dec. 2006.

- [21] J. Rogers and C. Plett, Radio Frequency Integrated Circuit Design. Norwood, MA, USA: Artech House, 2003.

- [22] Y. Chen, "Innovative design and realization of microwave and millimeter-wave integrated circuits," Ph.D. dissertation, Dept. Elect. Comput. Eng., Nat. Univ., San Diego, CA, USA, 2011.

- [23] Y. Chen and M. Geurts, "A Gilbert mixer including decoupling means," Eur. Patent 2458729A1, May 30, 2012.

- [24] H.-K. Chiou, K.-C. Lin, W.-H. Chen, and Y.-Z. Juang, "A 1-V 5-GHz self-bias folded-switch mixer in 90-nm CMOS for WLAN receiver," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 6, pp. 1215–1227, Jun. 2011

- [25] D. Ahn, D.-W. Kim, and S. Hong, "A K-band high-gain down-conversion mixer in 0.18 μm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 4, pp. 227–229, Apr. 2009.

- [26] S. Ziabakhsh, M. Nirouei, A. Saberkari, and H. Alavi-Rad, "Reduction parasitic capacitance in switching stage RF-CMOS Gilbert mixer for 2.4 GHz application," in *Proc. IEEE 16th Int. Conf. Electron., Circuits,* Syst., Dec. 2009, pp. 615–618.

- [27] G. H. Tan, R. M. Sidek, M. M. Isa, and S. Shafie, "A low-power current bleeding mixer with improved LO-RF isolation for ZigBee application," in *Proc. IEEE Int. Conf. Circuits Syst.*, Sep. 2013, pp. 111–113.

- [28] H. Darabi and A. A. Abidi, "Noise in RF-CMOS mixers: A simple physical model," *IEEE J. Solid-State Circuits*, vol. 35, no. 1, pp. 15–25, Jan. 2000.

- [29] T. W. Kim, "A common-gate amplifier with transconductance non-linearity cancellation and its high-frequency analysis using the Volterra series," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 6, pp. 1461–1469, Jun. 2009.

- [30] C.-H. Chang and M. Onabajo, "Linearization of subthreshold lownoise amplifiers," in *Proc. IEEE Int. Symp. Circuit Syst.*, May 2013, pp. 377–380.

- [31] J. Yoon *et al.*, "A new RF CMOS Gilbert mixer with improved noise figure and linearity," *IEEE Trans. Microw. Theory Techn.*, vol. 56, no. 3, pp. 626–631, Mar. 2008.

- [32] C. H. Chen, P. Y. Chiang, and C. F. Jou, "A low voltage mixer with improved noise figure," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 2, pp. 92–94, Feb. 2009.

- [33] A. V. Do, C. C. Boon, M. A. Do, K. S. Yeo, and A. Cabuk, "A subthreshold low-noise amplifier optimized for ultra-low-power applications in the ISM band," *IEEE Trans. Microw. Theory Techn.*, vol. 56, no. 2, pp. 286–292, Feb. 2008.

- [34] D. Na and T. W. Kim, "A 1.2 V, 0.87–3.7 GHz wideband low-noise mixer using a current mirror for multiband application," *IEEE Microw. Wireless Compon. Lett.*, vol. 22, no. 2, pp. 91–93, Feb. 2012.

- [35] S. He and C. E. Saavedra, "An ultra-low-voltage and low-power ×2 subharmonic downconverter mixer," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 2, pp. 311–317, Feb. 2012.

- [36] W. K. Chong, H. Ramiah, and N. Vitee, "A 0.12-mm<sup>2</sup> 2.4-GHz CMOS inductorless high isolation subharmonic mixer with effective current-reuse transconductance," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 8, pp. 2427–2437, Aug. 2015.

- [37] C.-W. Kim, H.-W. Son, and B.-S. Kang, "A 2.4 GHz current-reused CMOS balun-mixer," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 7, pp. 464–466, Jul. 2009.

- [38] M.-J. Zeng, R.-Y. Huuang, and R.-M. Weng, "A 0.8V 8 GHz low power sub-harmonic self-oscillating mixer," in *Proc. IEEE Int. Symp. Circuits* Syst., Jun. 2014, pp. 1376–1379.

- [39] K.-H. Liang, H.-Y. Chang, and Y.-J. Chan, "A 0.5–7.5 GHz ultra low-voltage low-power mixer using bulk-injection method by 0.18-μm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 7, pp. 531–533, Jul. 2007.

Gim Heng Tan received the B.Sc., M.Sc., and Ph.D. degrees in electronic engineering from University Putra Malaysia, Selangor, Malaysia, in 1999, 2001, and 2015, respectively.

He was a Design Engineer with Malaysia Microelectronic Solution, Selangor, and an Assistant Design Manager with the Sires Labs Sdn Bhd, Selangor, from 2001 to 2009. He is currently a Senior Lecturer with the Electrical and Electronic Engineering Department, Infrastructure University Kuala Lumpur, Kuala Lumpur, Malaysia. His

research has resulted into various technical publications. His current research interests include power management chips, data converter, optical transceiver, and radio frequency integrated circuit design.

Harikrishnan Ramiah (M'10–SM'15) received the B.Eng. (Hons.), M.Sc., and Ph.D. degrees in electrical and electronic engineering (with a specialization in analog and digital IC design) from Universiti Sains, Penang, Malaysia, in 2000, 2003, and 2008, respectively.

In 2002, he joined Intel Technology Sdn. Bhd., Penang, where he was involved in power gating solution of 45-nm process high-frequency signal integrity analysis for high-speed digital data transmission and developing MATLAB spread sheets for

eye diagram generation to evaluate signal response for FCBGA and FCMMAP packages. In 2003, he joined the Sires Labs Sdn. Bhd., CyberJaya, Malaysia, where he was involved in 10-Gb/s SONET/SDH transceiver solutions. He is currently an Associate Professor with the Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia, where he is involved in the area of RFIC design. His research work has resulted in several technical publications. His current research interests include analog integrated circuit design, RFIC design, very large scale integration system design, and RF energy harvesting power management module design.

Dr. Ramiah is a member of The Institute of Electronics, Information and Communication Engineers. He is currently a Chartered Engineer with the Institute of Electrical Technology and a registered Professional Engineer under the Board of Engineers, Malaysia. He was a recipient of the Intel Fellowship Grant Award in 2000–2008.

**Pui-In Mak** (S'00–M'08–SM'11) received the Ph.D. degree from the University of Macau (UM), Macau, China, in 2006.

He is currently an Associate Professor with UM, where he is also an Associate Director with the State Key Laboratory of Analog and Mixed-Signal VLSI. His current research interests include analog and RF circuits and systems for wireless, biomedical, and physical chemistry applications.

Prof. Mak was a member of the Board-of-Governors of the IEEE Circuits and Systems Society

from 2009 to 2011 and an Editorial Board member of the IEEE Press from 2014 to 2016. He was a recipient of the IEEE DAC/ISSCC Student Paper Award in 2002, the IEEE CASS Outstanding Young Author Award in 2010, the National Scientific and Technological Progress Award in 2011, and the Best Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS from 2012 to 2013. In 2005, he received the Honorary Title of Value for scientific merits by the Macau Government. He was a Senior Editor of the IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS from 2014 to 2015, an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS from 2010 to 2011 and in 2014, an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS from 2010 to 2013, and a Guest Editor of the IEEE RFIC VIRTUAL JOURNAL in 2014. He was a Distinguished Lecturer from 2014 to 2015.

**Rui P. Martins** (M'88–SM'99–F'08) was born in 1957. He received the bachelor's, master's, Ph.D., and Habilitation degrees in electrical engineering and computers from the Department of Electrical and Computer Engineering (DECE), Instituto Superior Técnico (IST), Technical University of Lisbon, Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

From 1980 to 1992, he was with DECE, IST, where he later became a Full Professor. From 1994 to 1997, he was the Dean with the Faculty of Science

and Technology (FST), University of Macau (UM), Macau, China, where he has been the Vice-Rector since 1997. Since 2013, he has been with the Department of Electrical and Computer Engineering, FST, where he is currently a Chair-Professor. He has taught 21 bachelor's and master's courses and has supervised (or co-supervised) 39 theses, Ph.D. (18), and master's (21). He was a Co-Founder of Chipidea Microelectronics (now Synopsys), Macau, from 2001 to 2002. He created the Analog and Mixed-Signal VLSI Research Laboratory at UM in 2003, which was elevated to the State Key Laboratory of China (the first in Engineering in Macau) in 2011, of which he was the Founding Director. He has co-authored 6 books and 5 book chapters and holds 18 patents, U.S. (16) and Taiwan (2). He has authored or co-authored 326 papers, in scientific journals (85) and in conference proceedings (241), as well as 61 other academic works, in a total of 416 publications.

Prof. Martins was a corresponding member of the Portuguese Academy of Sciences, Lisbon, in 2010, and a member of the IEEE CASS Fellow Evaluation Committee from 2013 to 2014. He received the Medal of Professional Merit from the Macao Government (Portuguese Administration) in 1999 and the Honorary Title of Value from the Macao SAR Government (Chinese Administration) in 2001. He was the founding Chairman of the IEEE Macau Section from 2003 to 2005 and of the IEEE Macau Joint-Chapter on Circuits And Systems (CAS)/Communications (COM) from 2005 to 2008 [2009 World Chapter of the Year of the IEEE Circuits And Systems Society (CASS)]. He was the General Chair of the 2008 IEEE Asia-Pacific Conference on CAS-APCCAS 2008, and was the Vice President of the Region 10 (Asia, Australia, and the Pacific) of the IEEE CAS Society from 2009 to 2011. He is currently the General Chair of the Asia South Pacific Design Automation Conference-ASP-DAC-2016. He was the Vice President of (World) Regional Activities and a member of the IEEE CAS Society from 2012 to 2013, an Associate Editor of the IEEE TRANS-ACTIONS ON SYSTEMS-II: EXPRESS BRIEFS from 2010 to 2013, and nominated as the Best Associate Editor of SYSTEMS-II: EXPRESS BRIEFS in 2012-2013. He was the CAS Society representative in the Nominating Committee, for the election in 2014, of the Division I (CASS/EDS/SSCS)-Director of the IEEE.