# 3º Simpósio de Electrónica das Telecomunicações

Porto, 4-6 Maio 1988.

## **COMPONENTES PARA CIRCUITOS INTEGRADOS CMOS COM CONDENSADORES COMUTADOS**

R. Martins<sup>1</sup>, J. Franca<sup>1</sup>, C. Leme<sup>1</sup>, J. Vital<sup>1</sup>, F. Maloberti<sup>2</sup>

1- Centro de Electrónica Aplicada da Universidade Técnica de Lisboa e Departamento de Engenharia Electrotécnica e de Computadores do Instituto Superior Técnico, Lisboa. 2- Dipartimento di Elettronica, Università degli Studi di Pavia, Pavia, Itália.

#### Abstract

Switched-Capacitor(SC) circuits play an important role in many analogue signal processing applications and are particularly attractive for Very Large Scale Integration(VLSI). This paper describes the design and Integrated Circuit(IC) implementation of basic SC circuit components, such as Operational Amplifiers (OA's), analogue transmission gates, a voltage comparator and high precision capacitor arrays. The IC implementation of these components has been realised using 3  $\mu m$  and 1.5  $\mu m$  analogue CMOS technologies.

#### Sumario

Os circuitos e sistemas com condensadores comutados desempenham um importante papel em muitas aplicações de processamento de sinal analógico, sendo particularmente atractiva a sua utilização em sistemas de integração em muito larga escala (VLST). Este artigo descreve o projecto e realização em circuito integrado dos componentes básicos de circuitos com condensadores comutados, tais como amplificadores operacionais, portas de transmissão analógicas, um comparador de tensão e agregados de condensadores de elevada precisão. A implementação em circuito integrado monolítico deste tipo de componentes foi realizada com tecnologias analógicas CMOS de 3 µm e 1.5 µm.

#### 1. INTRODUCÃO.

Nos últimos anos tem-se assistido a uma evolução constante das técnicas de realização de circuitos integrados monolíticos, que permitem a integração de sistemas cada vez mais complexos [1,2]. Os sistemas digitais, não exigindo características dos sistemas cada vez mais complexos [1,2]. Os sistemas digitais, não exigindo características dos dispositivos muito precisas, são facilmente integráveis e têm progredido rapidamente. Os sistemas analógicos, exigindo uma maior precisão das características dos dispositivos, têm tido uma evolução mais lenta, conseguida através de avanços feitos nas técnicas de projecto dos circuitos e no refinamento dos processos de fabrico dos circuitos integrados.

feitos nas técnicas de projecto dos circuitos e no refinamento dos processos de fabrico dos circuitos integrados.

Até há pouco tempo, os sistemas electrônicos eram geralmente implementados utilizando componentes analógicos fabricados em tecnologia bipolar, para a realização das partes analógicas, e dispositivos MOS-LSI para a realização das partes digitais. À medida que foram sendo atingidos niveis cada vez mais altos de integração (LSI e VLSI), a utilização de circuitos integração (LSI e VLSI), a utilização de circuitos integração analógicos e digitais distintos tornou-se complicada e cara. Surge assim, a motivação para o fabrico das partes analógicas e digitail no mesmo circuito integrado e com a mesma tecnologia. Dado que as tecnologias LSI e VLSI utilizadas até agora são a NMOS e CMOS, tradicionalmente digitais, tornou-se necessária a realização de funções analógicas usando também estas tecnologias.

Os circuitos com condensadores comutados constituem uma das técnicas preferenciais para a realização de circuitos integrados analógicos ou mistos analógicos-digitais. A importância destes circuitos resulta do facto de serem compatíveis com as tecnologias microelectrónicas NMOS e CMOS para a realização de circuitos VLSI, permitindo deste modo a implementação num único circuito integrado de sistemas complexos de processamento de sinal que contenham simultaneamente funcões analógicas e digitais [3,4]. A esta fácil capacidade de integração encontram-se

associadas a possibilidade de realização de funções de processamento de sinal de elevada qualidade e ainda a implementação de funções analógicas com a versatilidade de programação tipica dos circuitos digitais. A elevada qualidade destes circuitos advém do facto de os seus parâmetros essenciais serem determinados por sinais de relógio extremamente precisos e por relações de capacidades definidas por processos geométricos e litográficos igualmente de grande precisão.

Os transistores e condensadores constituem os

grande precisao.

Os transistores e condensadores constituem os elementos básicos da tecnologia de circúitos com condensadores comutados, podendo um circuito integrado analógico conter, tipicamente, de poucas dezenas a várias dezenas ou mesmo centenas de milhar de analógico conter, tipicamente, de poucas dezenas a várias dezenas ou mesmo centenas de milhar de transistores e igualmente um número bastante elevado de condensadores. Os Amplificadores Operacionais (AO's), comparadores de tensão, portas de transmissão analógicas e agregados de condensadores constituem alguns dos componentes de circuito que podem ser realizados através do agrupamento de elementos básicos. Estes componentes de circuito agrupados de acordo com determinado objectivo dão origem aos circuitos básicos que poderão ser utilizados em aplicações lineares de filtragem, decimação e interpolação (se forem constituidos por amplificadores operacionais, portas de transmissão analógicas e condensadores) (5,8), ou ainda em aplicações não-lineares de rectificação, modulação e conversão de sinal A/D e D/A (se possuirem comparadores de tensão, fontes de tensão de referência, condensadores e agregados de condensadores) (9,10). Finalmente, os sistemas de processamento de sinal com condensadores comutados são constituidos por diversos circuitos básicos de acordo com as características exigidas em cada aplicação (11,12).

### 2. AMPLIFICADORES OPERACIONAIS.

O amplificador operacional é um dos componentes mais importantes dos circuitos com condensadores comutados. Deve possuir ganho elevado, com acoplamento em corrente continua e com resposta em frequência em corrente continha e com resposta em frequência controlada, quando necessário, através dum circuito de realimentação. Considerado o circuito analógico linear básico, o AO é usado numa grande variedade de funções lineares, e por vezes algumas não-lineares. As características do AO ideal são: ganho DC infinito, impedância de entrada infinita e impedância de saída nula. Embora os AO's reais não possuam estas características, o seu ganho em baixa frequência é ainda bastante elevado, de tal modo que na maioria das aplicações o comportamento do circuito real se aproxima do AO ideal.

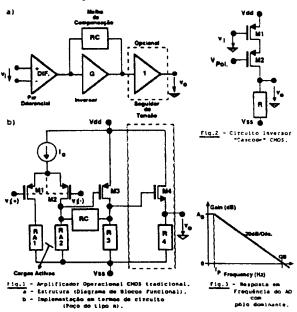

Estrutura e Implementação Tradicionais: A estrutura básica e a implementação tradicional de um AO realizado com tecnologia CMOS, encontram-se representadas nas Figs.1-a,b. O andar de ganho diferencial, também designado par diferencial, tem como objectivos principais a obtenção de ganho e impedância de entrada diferenciais elevados e ainda a conversão de entrada diferencial-saída simples (com um dos terminais à massa) que permita o correcto acoplamento ao andar seguinte. O ganho de tensão diferencial deste andar é dado por andar é dado por

$$G_{DIP} = -g_{n} R_{0} \tag{1}$$

em que

$$g_{n} = 2 \sqrt{K (I_{0}/2) (1+\lambda V_{05})}$$

(2)

$$R_0 = \frac{1 + \lambda V_{0S}}{\lambda (I_0/2)} \tag{3}$$

sendo lum parâmetro relacionado com a modulação do comprimento de canal dos transistores MOS e em que

$$K = \frac{(\mu_0 C_{DX})}{2} \left( \frac{W}{L} \right) \tag{4}$$

é uma constante relacionada com a geometria e as características desses mesmos transistores. Na expressão anterior,  $\mu_0$  representa a mobilidade superficial média dos electrões no canal,  $C_{\rm ox}$  é a superricial media dos electroes no canal, C<sub>OX</sub> & a capacidade do óxido por unidade de área e (W/L) descreve a geometria (Largura//Comprimento) do canal dos transistores MOS (1,3,13]. O andar de ganho habitualmente constítuido por um circuito inversor, como se representa igualmente na Fig.l-b, deve permitir a obtenção do ganho elevado necessário ao correcto funcionamento do AO. Para reforçar o ganho dos andares inversores é vulgar utilizarem-se transistores compostos em montagem "Cascode", tal como se apresenta na Fig.2. Neste caso o ganho vem dado por

$$G_{z-cAd} = -g_{m1} R_{o2} (1+g_{m2}R_{o1})$$

(5)

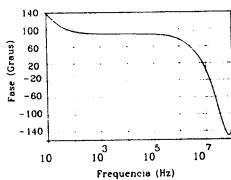

em que o factor multiplicativo (1+ $g_{m2}R_{01}$ ) resulta da em que o factor multiplicativo (1+g<sub>m2</sub>R<sub>01</sub>) resulta da configuração "Cascode" utilizada. A malha de compensação presente igualmente na Fig.1, pode ser constituida por um simples condensador ou por uma resistência (simulada por um transistor MOS) em série com um condensador, de modo a tornar o AO uma estrutura de pólo dominante cuja resposta em frequência se deve apresentar como na Fig.3 [13]. Se o andar de ganho for uma montagem "Cascode" a impedância de saida será muito elevada pelo que o AO é compensado apenas com a colocação de um condensador na saida (C). apenas com a colocação de um condensador na saida  $(C_L)$ . Neste caso o polo dominante de baixa frequência será dado por

$$\mathbf{F_0} = \frac{1}{2 \times R_0 C_L} \tag{6}$$

donde resulta igualmente um produto ganho-largura de banda elevado que permite aplicações em alta frequência. Devido ao nó de saída do andar de ganho ser um ponto de alta impedância será necessário, em algumas aplicações com cargas de valor elevado, a colocação de um andar adicional de saída que actuará como circuito tampão e que poderá ser constituido por um simples seguidor de tensão, como também se pode varrificar na Fig 1 verificar na Fig.1.

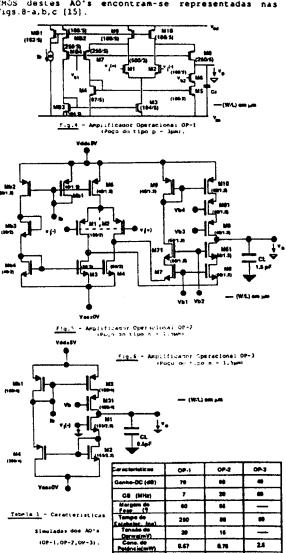

AO's para Utilização em Alta Frequência: Os circuitos com condensadores comutados, possuindo apenas cargas puramente capacitivas permitem a utilização de AO's com elevada impedância de saida pelo que se torna possível projectar AO's com um único andar em tecnologia CMOS com ganho e largura de banda bastante elevados. Um AO deste tipo é designado por "Folded Cascode" e é constituído por um andar diferencial e um andar de ganho "Cascode" que do ponto

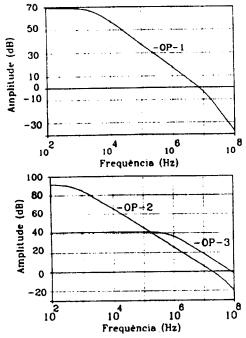

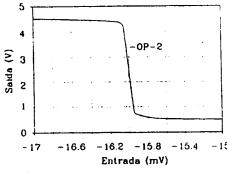

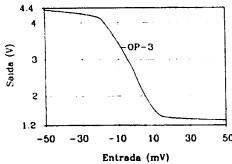

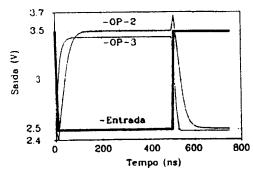

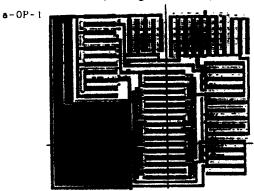

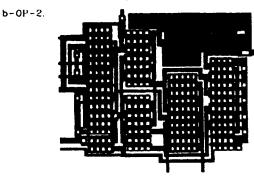

de vista incremental se comportam como um único andar. Este tipo de AO possui um produto ganho-largura de banda bastante elevado e de igual modo a sua alta impedancia de saida impõe um polo dominante a muito baixa frequência como em (6). As estruturas de dois AO's deste tipo designados por OP-1 e OP-2 encontram-se representadas nas Figs. 4 e 5, respectivamente. Alem do andar diferencial e "andar "ascode" estão ainda representados os diferentes "ircuitos de polarização que são essencialmente "uspelhos de corrente" e fontes de tensão de referência [13]. Estes AO's foram realizados com diferentes tecnologias CMOS (OP-1-3µm, OP-2-1.5µm) e as suas caracteristicas obtidas por simulação em computador [14] encontram-se na Tabela-1. De modo a aumentar ainda mais o ganho de tensão DC do AO foram colocados transistores adicionais no "andar de ganho Cascode" de OP-2, que pode ser visto como um "andar de ganho Cascode" de OP-2, que pode ser visto como um "andar de ganho Cascode" de OP-2, se pode ser visto como um "andar de ganho Cascode" de OP-2, se pode, 20MH2). Outro tipo de estrutura de AO baseado apenas num inversor "Cascode" e apresentado na Fig.6, sendo designado por OP-3. As suas características são igualmente dadas na Tabela 1. Este AO apresenta um ganho de tensão DC relativamente baixo (40 dB) mas uma largura de banda muito elevada (90 MHz) com um tempo de estabelecimento ("setiling time") perto dos 50ns, o que o torna bastante rápido e adequado para aplicações de alta frequência pouco sensiveis ao valor do ganho [8]. Na Fig.7 são apresentadas as simulações em computador [14] da resposta em frequência, resposta a um escalão unitário e característica de transferência de tensão destes amplificadores. As implantações em circuito integrado CMOS destes AO's encontram-se representadas nas Figs.8-a,b,c [15].

# Resposta em frequência

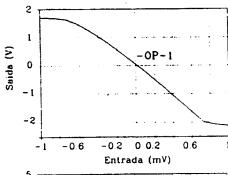

Característica de transferência de tensão

## Resposta ao escalão unitário

Fig.7 - Características simuladas dos AO's. Resposta em frequência, Característica de transferência de tensão, Resposta ao escalão unitário (montagem inversora).

Fig 8 - Implantação em Circuito Integrado. a-OP-1. b-OP-2. c-OP-3.

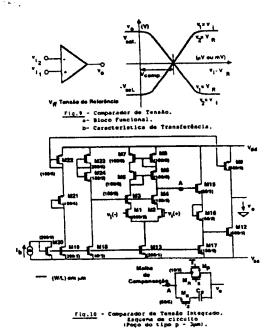

#### 3. COMPARADOR DE TENSÃO.

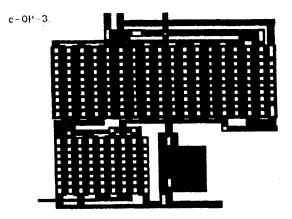

O comparador de tensão é um dos componentes de circuito mais utilizado em aplicações não lineares com condensadores comutados. Pode ser considerado um AO especializado que permite a comparação de um sinal de entrada  $\mathbf{v}_i$  (t) com uma tensão de referência  $\mathbf{V}_R$  (estrutura na Fig.9-a) e cuja característica típica de transferência se apresenta na Fig.9-b. Deve permitir mudanças rápidas de tensão na saida com pequenas variações da tensão de entrada em torno da tensão de referência. Deste modo, a sua tensão de desvio ("offset") na entrada deve ser muito reduzida uma vez que contribui com um erro no ponto de comparação de  $\mathbf{v}_i$  (t) e  $\mathbf{v}_s$ .

Que contribui com um esto no posito de comparação de tensão utilizado num circuito de um comparador de tensão utilizado num circuito conversor A/D e D/A de alta resolução [9]. Durante o ciclo de conversão A/D, o comparador deve distinguir 90µV ((1/2)LSB-"Least Significant Bit") em menos de lµs para que o ritmo de conversão seja elevado. No ciclo de calibração não é muito crítico o tempo de conversão, mas o comparador deve poder distinguir cerca de 23µV ((1/8)LSB). As caracteristicas necessárias à conversão D/A são menos exigentes, com 2µs de tempo de estabelecimento e 180µV de erro no valor final da tensão, devendo a gama de tensão de sida ser de 6V (-3V a 3V). Para cumprir estas especificações, o circuito apresentado possui um andar diferencial configurado como andar "Cascode" (com carga activa "Cascode) para permitir a obtenção de ganho e larqura de banda elevados. O ganho adicional necessário é conseguido através do andar inversor na saida constituido pelos transistores M<sub>0</sub> e M<sub>12</sub> sendo o acoplamento entre estes dois andares realizado através do circuito de ajuste de nível de tensão composto por M<sub>15</sub> e M<sub>16</sub> ("Level Shifter"). A compensação da resposta em frequência é conseguida através da malha Crealizada com o condensador C<sub>C</sub> e o transistor M<sub>C</sub> (que realiza a resistência R<sub>C</sub>) e efectua o desvio do primeiro pólo para uma frequência ainda mais baixa ("pole spliting") acompanhado do cancelamento do segundo pólo de modo a tornar o comparador uma estrutura de pólo dominante. Esta malha de compensação não se encontra activa durante a operação de comparação (transitor M<sub>C</sub> desligado-Fase z) para ser mais rápida a resposta do comparador num estado de auto-polarização, sendo fechado por um periodo de 250ns imediatamente antes da operação de comparação (Fase x), permitindo retirar o comparador num estado de saturação e reduzir o tempo de resposta. As características príncipais deste comparador de tensão obtidas por simulação (14) encontram-se na Tabela 2 estando representadas na Fig.11 as curvas de resposta em

| Coroctoristicos<br>Comparador de Yonado               |                   |  |  |  |

|-------------------------------------------------------|-------------------|--|--|--|

| Tenados do<br>Alimentação                             | ) SV              |  |  |  |

| Received                                              | 30 <sub>+</sub> V |  |  |  |

| Tempe de Estaboles. (µ4)                              |                   |  |  |  |

| Compone. QH                                           | 1.6               |  |  |  |

| Compone. OFF                                          | 0.0               |  |  |  |

| Auto-Zero                                             | 10                |  |  |  |

| Cons. de<br>Petáncia(mW)                              | 10                |  |  |  |

| Area CI (µm ) 2                                       | 77 Sa 220         |  |  |  |

| 1: n g ? - Caracteristicas :<br>Comparador de Tensão. |                   |  |  |  |

|   |   |    | - 1 | : 4 |    | 4. |   |  |

|---|---|----|-----|-----|----|----|---|--|

| • | - | Am | D١  | и   | .u | u  | Ľ |  |

|                | Frequência (Hz) |   |     |     |          |  |  |

|----------------|-----------------|---|-----|-----|----------|--|--|

|                | 10              | ) | 103 | 105 | 10       |  |  |

|                | -60             |   |     |     |          |  |  |

|                | -40             |   |     |     | - \      |  |  |

| Ē              | -20<br>-40      |   | . : |     |          |  |  |

| Ξ              | 0               |   |     |     |          |  |  |

| ď              | 20              | - | •   |     | <u> </u> |  |  |

| Amplitude (dB) | 60<br>40        |   |     |     |          |  |  |

| _              | 80              |   |     |     | •        |  |  |

|                | 100             |   | -   |     |          |  |  |

| 711            | piica           | • |     |     |          |  |  |

b - Fase.

Fig 11 - Resposta em frequência do Comparador de Tensão.

a- Amplitude. b- Fase.

Fig.12 - Implantação em Circuito Integrado do Comparador de Tensão.

# 4. RAMOS DE CIRCUITO COM CONDENSADORES COMUTADOS.

Os ramos passivos básicos dos circuitos com condensadores comutados são constituidos por portas de transmissão analógicas, que são transistores actuando como interruptores, e condensadores. Embora do ponto de vista de análise do circuito possam ser considerados elementos ideais, apresentam certos desvios da idealidade caracterizados por uma resistência de condução (R<sub>ON</sub>) finita e um tempo de comutação não instantâneo que se revelam ser de grande importância em aplicações de alta e muito alta frequência.

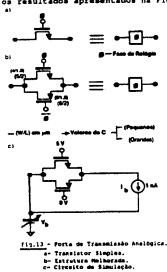

Portas de Transmissão Analógicas: Uma porta de transmissão analógica pode ser realizada por um único transistor funcionando como interruptor, como na Fig.13-a. No entanto de modo a permitir uma elevada velocidade de operação aliada a um baixo valor de R<sub>ON</sub>

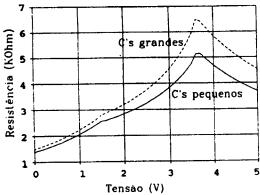

deve ser adoptada uma estrutura de circuito como a que se apresenta na Fig.13-b. As dimensões dos transistores devem ser adaptadas aos circuitos em que estas portas analógicas estão inseridas, sendo possível utilizar transistores com dimensões minimas quando os condensadores presentes têm baixo valor de capacidade. Se, no entanto, o circuito possuir condensadores de capacidade elevada sendo precisos tempos de resposta muito reduzidos que implicam correntes elevadas, torna-se necessário aumentar as dimensões dos transistores mantendo o valor de R<sub>ON</sub> o mais baixo possível. Este valor de R<sub>ON</sub> (variável com a tensão) foi avaliado para as duas portas analógicas da Fig.13-b a partir da simulação do circuito da Fig.13-c [14], sendo os resultados apresentados na Fig.14.

Fig.14 - Simulação das Portas Analógicas da Fig.13-b.

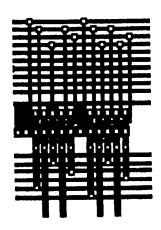

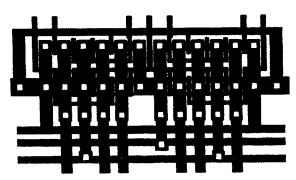

Ramos Insensiveis às Capacidades Parasitas: As portas de transmissão analógicas podem ser agrupadas e ligadas a condensadores de modo a constituirem ramos insensíveis às capacidades parasitas [16]. Estes ramos podem realizar diferentes estruturas como as que se apresentam na Fig.15-a,b,c,d. Na Fig.16-a,b encontra-se representada a implantação em circuito integrado CMOS (tecnologia de 1.5µm) de agregados deste tipo de ramos. A Fig.16-a apresenta ramos do tipo PCTSC (Fig.15-c) realizados com as portas analógicas de dimensões minimas já referidas (Fig.13-b) e que constituem a secção de entrada de um decimador de alta frequência com condensadores comutados (8]. Na Fig.16-b, os ramos do tipo TSI e OFR (Fig.15-a,b, respectivamente) fazem parte duma estrutura de dois integradores num laco fechado que realizam a parte recursiva do mesmo decimador e apresentam portas analógicas de maiores dimensões (Fig.13-b) devido a se encontrarem ligados a capacidades elevadas.

Fig.15 - Ramos com Condensadores Comutados. 4- TSI, b- OFR, c- PCTSC (Neg.) d- PCTSC (Pus.)

## a- TSI e OFR

b- Agregado PCTSC (Neg.).

Fig.16 - Implantação em Circuito Integrado de Ramos com Condensadores Comutados.

a- TSI e OFR. b- Agregado de Ramos PCTSC (Neg.).

## 5. CONDENSADORES E AGREGADOS DE CONDENSADORES.

S. CONDENSADORES E AGREGADOS DE CONDENSADORES.

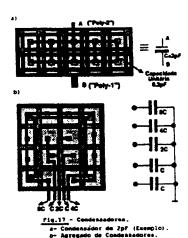

Os condensadores em tecnología CMOS de dupla camada de polisilicio ("double-poly") são realizados pela sobreposição de duas camadas de polisilicio, separadas por um dieléctrico de ôxido grosso. A área da placa superior do condensador ("top plate") determina o valor da capacidade. Em aplicações em que a precisão do valor das capacidades seya factor importante (0.1% ou 0.2%) torna-se necessário realizar as capacidades com um anel de guarda ("guard ring") circundando a camada superior de polisilicio, o que permite minimizar imprecisões na definição da área. Pela mesma razão, os valores de capacidades elevados são obtidos a partir do agrupamento de capacidades de valor unitário com as características anteriores, como exemplificado na Fig.17-a para um condensador de 2pF (supondo uma capacidade unitária de 0.2pF). Na Fig.17-b apresenta-se um agregado de condensadores constituido pela associação de capacidades unitárias numa configuração com simetria radial ("common centroid") que minimiza os efeitos do gradiente da espessura do ôxido grosso e a corrosão irregular. A implantação em circuito integrado deste agregado de condensadores encontra-se representada na Fig.18, para uma capacidade de 64pF que ocupa uma área de 500x500 μm².

Fig. 18 - Implantação de um Agregado de Condensadores em Circuito Integrado.

#### 6. CONCLUSÕES.

Neste artigo apresentam-se diversos componentes básicos utilizados em circuitos integrados CMOS com condensadores comutados. São descritos os projectos de vários amplificadores operacionais de elevado desempenho, de um comparador de tensão, de portas de transmissão analógicas, condensadores e agregados de condensadores. A implantação destes componentes em circuito integrado é apresentada utilizando tecnologias analógicas CMOS de 3µm e 1.5µm. Estes componentes são utilizados num grande número de aplicações de circuitos com condensadores comutados, tais como filtros, decimadores e conversores A/D e D/A. Neste artigo apresentam-se diversos componentes

#### Referências

- [1] C.MEAD, L.CONWAY, "Introduction to VLSI Systems", Addison-

- -Mesley, 1980.

N. MESTE, K.ESHRAGHIAN, "Principles of CNOS VLSI Design A Systems Perspective", And ison-Mesley, 1985.

R. GREGORIAN, G. TEMES, "Analog MOS Integrated Circuits for

- Signal Processing", Wiley-Interscience, 1986.

K.NAKAYAMA, Y.KURATSHI, "Present and Future Applications of

- K.NAKAYAMA, Y.KURATSHI, "Present and Future Applications of Switched-Capacitor Circuits", IEEE Circuits and Devices Magazine, pp.10-21, Setembro 1987.

P.FLEISCHER, K.LAMER, "A Family of Active Switched-Capacitor Biquad Building Blocks", Bell Systems Technical Journal, vol.58, No.12, pp.2235-2268, 1979.

G.MOSCHYIZ, "MOS Switched-Capacitor Filters:Analysis and Design", IEEE Press Selected Reprint Series, 1984.

J.FRANCA, "Non-Recursive Polypnase Switched-Capacitor Decimators and Interpolators", IEEE Transactions on Circuits and Systems, vol.CAS-32, No.9, pp.877-887, Setembro 1985.

R. MARTINS, J.FRANCA, F.MALOBERTI, "Design and Implementation of a CMOS Integrated Cyrcuit SC Decimator for High Frequency

- R.MARTINS, J.FRANCA, F.MALOBERTI, "Design are implementation a CMOS Integrated Circuit SC Decimator for High Frequency Applications", 3° Simposio de Electrônica das Telecomunicações, Porto, Portugal, Maio 1988.

C.LEME, J.FRANCA, F.MALOBERTI, "An Integrated System with

- Multiplexed Analogue/Digital and Digital/Analogue Conversion

- Multiplexed Analogue/Digital and Digital/Analogue Conversion Functions\*, 3° Simpósio de Electrónica das Telecomunicações, Porto, Portugal, Maio 1988. [10] J.VITAL, J.FRAMCA, F. MALOMERTI, "An Integrated Algorithmic Digital-to-Analogue Convertor with FIR Filtering\*, 3° Simpósio de Electrónica das Telecomunicações, Porto, Portugal, Maio 1988.

- de Electronica das Telecomunicaçoss, porto, portogalment (Front)

K.NAKAYAMA et al., "A Single-Chip Line Equalizer System for Full Duplex Multi-bit Rate Digital Transmission", Proc. ICASSP'86, pp.1521-1524, 1986.

[12] F.RRUMMEMACHER, "A High-Resolution Capacitance-to-Frequency Converter", IEEE J. Solid State Circuits, vol.SC-20, pp.666-670,

- Junho 1985.

- Junho 1985.

[13] P.CRAT, "Basic MOS Operational Amplifier Design-An Overview",

Analog MOS Integrated Circuits, IEEE Press Selected Reprints

Series, Wiley, New-York, pp.28-49, Marco 1980.

[14] L.MAGEL, "SPICE2: A computer program to simulate semiconductor

c.rouits", ERL Memo.No.VCB/ERL M75/520, Majo 1975.

- 15, K.R. ILEN, G. ALLINOSEEY, \*KIC: A Graphics Editor for Integrated Circuits\*, University of California at Berkeley, 1980.

- 16, P.FLEISCHER, A.GANESAN, K.LAKER, "Parasitic-Compensated Switched-Capacitor Circuits", Electronics Letters, vol.17, No.24, pp. 929-931, 26th. Novembro 1981.