# A Programmable Switched-Capacitor A-DQS Frequency Downconverter for Two-Step Channel Selection Wireless Receiver

Pui-In Mak<sup>1</sup>, Seng-Pan U<sup>2</sup> and R.P. Martins<sup>3</sup>

Mixed-Signal VLSI Laboratory (MSVLSI)

University of Macau, Faculty of Science and Technology Avenida Padre Tomás Pereira, Taipa, Macau, China E-mails: 1-p.i.mak@ieee.org, 2 - benspu@umac.mo, 3 - rmartins@umac.mo

3 - On leave from Instituto Superior Técnico (IST), Lisbon, Portugal

## **ABSTRACT**

This paper presents a combined half- and full-delay switched-capacitor frequency downconverter with embedded channel selection function through a programmable analog-double quadrature sampling (A-DQS) technique. With such circuit operating in a complex low-IF wireless receiver back-end, the IF-to-baseband frequency down-conversion of the desired channel or its image can be effectively selected to the baseband to relax the settling time and phase noise requirements of the front-end frequency synthesizer. Moreover, such circuit also allows I/Q multiplexing for the following A/D converter and then minimizes the image problem due to I/Q mismatch. The prototype circuit is designed and verified in CADENCE<sup>TM</sup> environment with the parameters of a 0.35-µm CMOS process.

#### 1. Introduction

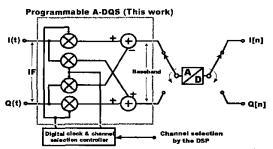

Complex low-IF wireless receivers [1-4] usually employ a very low intermediate frequency (IF) for quadrature frequency downconversion and to minimize the power consumption, as well as, to simplify the circuitry ahead. Thus, a double quadrature IF-to-baseband downconverter is still mandatory prior to signal digitization. Traditionally, a quadrature downconverter implemented by four mixers, which are driven by a quadrature local oscillator (LO) [5]. The problem of such architecture is there exists image interference due to unavoidable paths imbalance. Recently, analog-double quadrature sampling techniques (A-DQS) have been proposed for the double quadrature downconversion and channel selection. In this paper, two distinct switched-capacitor (SC) sample-and-hold (S/H) circuits, with half-delay or full-delay embedding the A-DQS, will be proposed. Their main advantages are: first, without much extra cost, the A/D converters with those S/Hs at the front-end will perform the IF-to-baseband downconversion. Second, to simplify the front-end frequency synthesizer [6] the channel selection can be divided into two steps [7-8]. Third, since such S/Hs achieve also a half- or full-delay, one double-sampled A/D converter can be utilized for the digitization of both channels (I and Q) through simple multiplexing. Then, the proposed complex low-IF receiver baseband structure will assume the format of Fig. 1.

**Figure 1:** Proposed baseband structure of complex low-IF receiver.

Next, in section 2, the A-DQS will be briefly reviewed followed by the circuit implementation in section 3. The simulation results will be provided in section 4, and finally section 5 will conclude this paper.

# 2. ANALOG-DOUBLE QUADRATURE SAMPLING

The operation of four sampling mixers in complex-to-complex frequency down-conversion is usually named analog-double quadrature sampling (A-DQS), which can be employed in the baseband of complex low-IF receivers for IF-to-baseband downconversion [7-10]. The main advantage is related with the sampling frequency  $f_s$  value, when it is equal to 4 times the IF and utilizing pseudo-differential circuit implementation, the mandatory multiplying values will be only 1, 0 or -1. Hence, in both channels (I and Q) the A-DQS can be effectively embedded in a pair of S/H circuits of the two A/D converters. Another feature of the A-DQS technique, explored in [6], is its frequency shifting characteristics that will allow the channel selection, and which imply also that, when the value of IF is set to half of the channel bandwidth the image and the desired channel will be neighbors. Thus, by utilizing forward/backward frequency the characteristics of the A-DQS, the downconverted channels can be selected between the desired channel or its adjacent one in the IF, through simple digital control on the S/Hs sampling sequences [11], to simplify the front-end voltage control oscillator (VCO) and frequency synthesizer settling time and phase noise requirements.

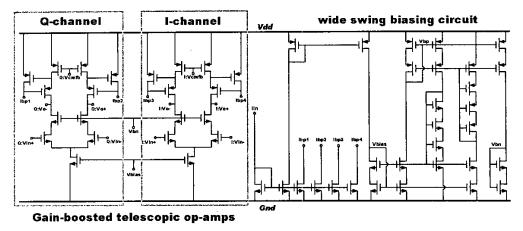

Figure 3: Schematic of the I and Q channels A-DQS S/Hs OTAs

#### 3. CIRCUIT IMPLEMENTATION

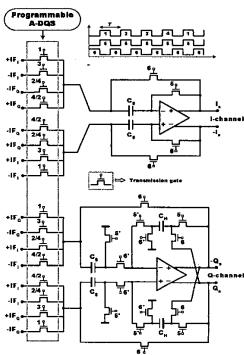

The prototype circuit of the A-DQS is implemented in 0.35-µm CMOS technology in CADENCE<sup>TM</sup> environment. In complex low-IF receiver, after the IF-to-baseband frequency down-conversion by the A-DQS, the desired channel at the baseband will be directly affected by the DC-offset and 1/f noise of the circuitries ahead. To minimize the effects of such switched-capacitor (SC) noise sources, two sample-and-hold circuits are used to realize such A-DQS, as shown in Fig. 2, with also the bottom-plate sampling technique. The half-delay S/H circuits not only possess a high feedback factor to minimize the required gain-bandwidth of the op-amp, but also inherently providing a transmission zero at DC to minimize the effect of those noises into the desired signal. The S/H with full-delay also possesses the transmission zero at DC due to the inversion of polarity in the holding phase. However, at the cost of requesting a higher slew-rate op-amp because the sampled value will start every period, between every positive and negative value. This half and full delay combined structure for the I and Q channels allows the utilization of one A/D converter to process both channels since the sampled output will be time-interleaved [The non-ideal transfer functions of both half and full-delay S/Hs will be presented later in the appendix]. The operational transconductance amplifiers (OTAs) for both I and Q channels are gain-boosted telescopic structure with a common wide swing biasing circuit for that will allow the reduction of chip-area and the increase of the matching. The common-mode feedback circuit uses switched-capacitor architecture to minimize the power consumption. The full circuit schematic is shown in Fig. 3 and its typical performance is listed in Table 1. All switches are implemented by transmission gates to minimize the distortion due to signal-dependent charge injection and also to increase the signal dynamic range. The dimensions of all the TGs are balanced having into consideration. 1/f noise, thermal noise. I/Q matching, settling time and clock

Figure 2: Half and full-delay combined A-DQS S/H circuits.

feedthrough. The clock phases and the channel selection controller can be obtained from [11].

Table 1: Performance of the OTA.

| 88.6dB  |

|---------|

| 207MHz  |

| 63.4°   |

| 113V/μs |

| 16.19ns |

| 1pF     |

| 1.46V   |

| 2.5V    |

|         |

Figure 4: Layout of the A-DQS S/H circuits.

#### 4. SIMULATION RESULTS

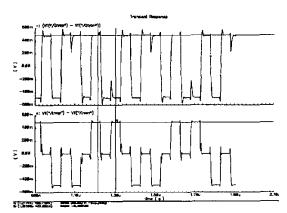

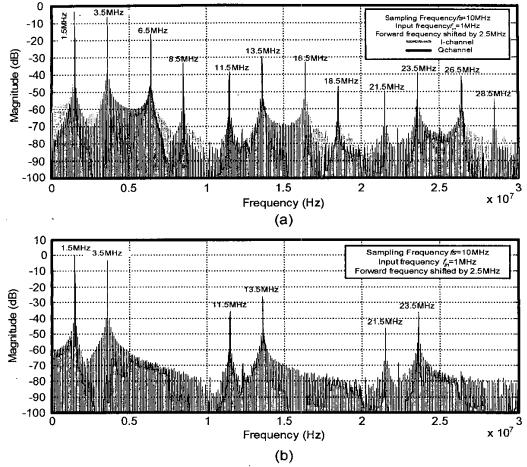

The layout of the proposed circuit is shown in Fig. 4 and the active chip-area is 0.17mm<sup>2</sup> (548x310µm) with total 5.05mW power dissipation at 2.5V power supply. The four sampling capacitors are implemented by double-poly with common-centroid geometry in the layout to reduce the non-linearity and mismatches. The simulation was conducted with a sampling frequency equal to 10MHz. The precision of the S/H circuit was tested through the application of a 500mV DC input voltage. After frequency shifting and sampling-and-holding through the A-DQS downconverter, the output held values are 498.718mV and 499.886mV, for the I Channel and the Q Channel, respectively, as shown in Fig. 5. For the frequency downconversion verification, and with the purpose of illustration, only the forward frequency shifting operation will be presented next. The simulated power spectrum densities (PSD) of both channels are shown in Fig 6a with a 1MHz sinusoidal input source. After sample-and-hold and frequency translation operations by A-DQS, the sampled 1MHz input signal is shifted by 2.5MHz (f<sub>s</sub>/4) and will have replicas located at  $\pm n1.5$ MHz.  $\pm n3.5$ MHz.  $\pm n6.5$ MHz and  $\pm n8.5$ MHz with n=1,2,3... The attenuation of their magnitudes is due to the sine response of the sample-and-hold process, and not due to the image-rejection in this case. For the complex PSD (|I+jQ|) that is shown in Fig. 6b, those signals at ±n6.5MHz and ±n8.5MHz with n=1, 2, 3.... are cancelled as the original phase difference between the I and Q channels are in quadrature.

# 5. CONCLUSIONS

A combined half- and full-delay SC sample-and-hold circuits has been presented for a complex low-IF receiver with embedding frequency downconversion and channel selection functions by utilizing the A-DQS. Such circuit can operate in the IF to perform a high-effective two-step channel selection to simplify

**Figure 5:** CADENCE<sup>TM</sup> transient simulation results of Q (upper) and I (lower) channels.

the front-end frequency synthesizer. Moreover, such circuit allows a single A/D converter for the I/Q digitization to minimize the I/Q mismatch and power consumption. The prototype circuit has been designed and verified in CADENCE<sup>TM</sup> environment with 0.35- $\mu$ m CMOS technology.

## 6. APPENDIX

Due to the op-amp finite gain A, voltage offset  $V_{os}$  and input parastic capacitance  $C_{in}$ , the non-ideal transfer function of the half-delay S/H circuit is given by

$$H(z) = \frac{C_S z^{-\frac{1}{2}}}{\left(C_S + \frac{C_S}{A} + \frac{C_{in}}{A}\right) - \left(\frac{C_S}{A} + \frac{C_{in}}{A}\right) z^{-\frac{1}{2}}}$$

(1)

The feedback factor is

$$\beta = \frac{C_S}{C_S + C_m} \tag{2}$$

The transfer function of the full-delay S/H circuit is

$$H(z) = -\frac{-C_S V_{in}(z) z^{-\frac{1}{2}}}{\left(1 + \frac{1}{A\beta_1}\right) \left(1 + \frac{1}{A\beta_2}\right)} + V_{OS} z^{-\frac{1}{2}} \left[ \frac{1 + \frac{C_{in}}{C_S}}{\left(1 + \frac{1}{A\beta_1}\right) \left(1 + \frac{1}{A\beta_2}\right)} - \frac{1 + \frac{C_{in}}{C_H}}{\cdot 1 + \frac{1}{A\beta_2}} \right]$$

(3)

with the feedback factors

$$\beta_1 = \frac{C_S}{C_S + C_P}, \beta_2 = \frac{C_H}{C_H + C_P}$$

(4-5)

Eq. 3 implies the offset error cannot be fully cancelled and a doubled DC gain would be required to achieve the same precision as the half-delay S/H architecture.

Figure 6: PSD of the A-DQS S/Hs outputs (a) I and Q channels (b) Complex response |I+jQ|.

# REFERENCES

- Michiel Steyaert, et al. "A Single-chip CMOS Transceiver for DCS-1800 Wireless Communications," IEEE ISSCC., Digest of Technical Papers, pp.48-49, FEBRUARY 1998.

- [2] Jan Crols and M. Steyaert, "Low-IF Topologies for High-Performance Analog Front Ends of Fully Integrated Receivers," *IEEE Transaction on Circuit* and System II: VOL. 45, NO. 3, MARCH 1998.

- [3] Michiel S.J. Steyaert, et al. "A 2V CMOS Cellular Transceiver Front-End," IEEE Journal of Solid-State Circuits, VOL. 35, NO. 12, DECEMBER 2000.

- [4] Wenjun Sheng, et al. "A 3-V 0.35-µm CMOS Bluetooth Receiver IC," IEEE Journal of Solid-State Circuits, VOL. 38, NO. 1, JANUARY 2003.

- [5] F. Behbahani, et al. "CMOS Mixers and Polyphase Filters for Large Image-rejection," IEEE Journal of Solid-State Circuits, VOL.36, NO.6, JUNE 2001.

- [6] Bram De Muer and M. Steyaaert, "Fully Integrated CMOS Frequency Synthesizers for wireless Communications" in Analog Circuit Design, p. 287-324, Kluwer Academic Publishers, 2000.

- [7] Pui-In Mak, et al. "A Novel IF channel Selection Technique by Analog- Double quadrature Sampling for Complex Low-IF Receivers," in Proceedings of Inter. Conf. on Communication Technology (ICCT), vol. 2, pp.1238-1241, Beijing, China, APRIL 2003.

- [8] Pui-In Mak, et al. "Two-step channel selection technique by Programmable digital-double quadrature sampling for complex low-IF receivers," Electronics Letters, vol. 39, no. 11, pp. 825-827, MAY 2003.

- [9] C. A. Leme, et al. "Wide-band Sub-Sampling A/D Conversion with Image-rejection," in *IEEE workshop* on Wireless Comm. Circuits and Systems, Lucerne, Switzerland, JUNE 1998.

- [10] K.P. Pun, et al. "A Quadrature Sampling Scheme with Improved Image-rejection for Complex-IF Receivers," in *IEEE ISCAS*, VOL. I, pp.45-48, MAY 2001.

- [11] Pui-In Mak, et al. "A Frequency-Downconversion and Channel Selection Sample-and-Hold circuit with A-DQS technique for Complex Low-IF Wireless Receivers," accepted in the 10th IEEE ICECS, United Arab Emirates, DECEMBER 2003.