## 17.2 A 0.0013mm<sup>2</sup> 3.6µW Nested-Current-Mirror Single-Stage Amplifier Driving 0.15-to-15nF Capacitive Loads with >62° Phase Margin

Zushu Yan<sup>1</sup>, Pui-In Mak<sup>1,2</sup>, Man-Kay Law<sup>1,2</sup>, Rui Martins<sup>1,2,3</sup>, Franco Maloberti<sup>4</sup>

<sup>1</sup>University of Macau, Macao, China, <sup>2</sup>UMTEC, Macao, China, <sup>3</sup>Instituto Superior Tecnico, Lisbon, Portugal, <sup>4</sup>University of Pavia, Pavia, Italy

For active-matrix LCDs [1] that have thousands of buffer amplifiers integrated in its column-driver ICs, ultra-low power and area circuit solutions are continuously urged to meet the market pressure on cost, image quality and display size. Multi-stage amplifiers have dominated those buffers due to their reliable DC gain, output swing, gain-bandwidth product (GBW) and slew rate (SR). Yet, different kinds of frequency compensation are also useful for stability, bottlenecking the capacitive-load ( $C_L$ ) drivability, power and area efficiencies.

Classical single-stage amplifiers were underused in those buffers due to their limited capability in most metrics despite being almost unconditionally stable at any C<sub>1</sub> and tiny in size. In view of this, it is beneficial to revisit the fundamental limits of single-stage amplifiers and deal with them differently. This paper introduces a nested-current-mirror (NCM) single-stage amplifier to advance its GBW-to-power/area efficiency and C<sub>1</sub> drivability beyond the multi-stage designs, while preserving a rail-to-rail output swing. The fabricated NCM amplifier demonstrates 33× higher GBW and 47dB higher DC gain than those of a typical differential-pair (DP) amplifier at equal power and area. By benchmarking with the recent three-stage amplifiers [2]-[4], this work improves FOM<sub>1</sub> [=GBW·C $_1$ /(Power·Area)] by >6.6×, and upholds a comparable FOM $_2$ [=SR·C<sub>L</sub>/(Power·Area)]. The C<sub>L</sub> drivability is >10× wider than [2]-[4], while avoiding the stability limit at the heavy-C<sub>L</sub> side. These results justify advanced single-stage amplifiers as a potential replacement for multi-stage designs in traditional (e.g. 100pF/m coaxial cable) and advanced (e.g. low temperature polysilicon LCD) buffer interfaces.

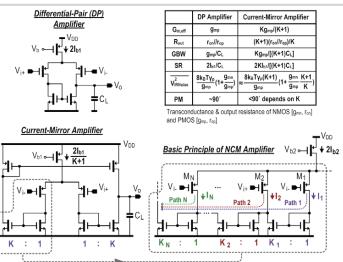

Most single-stage amplifiers suffer from a tight tradeoff between power and performance. Telescopic amplifiers feature a GBW-to-power efficiency as high as that of the DP amplifier (Fig. 17.2.1), but sacrifice output swing. Folded-cascode amplifiers partially surmount such a limit, but at the expense of power. For LCD column drivers, current-mirror amplifiers are favored for their rail-to-rail output swing, and extra design flexibility via adjusting the mirror ratio, K. A large K benefits most metrics (i.e., effective transconductance ( $G_{m,eff}$ ), GBW and SR), but at the expense of noise and phase margin (PM). Yet, no matter how large K is, most metrics of the current-mirror amplifier still lag behind those of the DP amplifier.

The basic principle of the NCM amplifier (Fig. 17.2.1) is to subdivide a current mirror into a number of pieces with different ratios, and sequentially combine their outputs to concurrently advance G<sub>m.eff</sub> and output resistance (R<sub>out</sub>) beyond those of the DP and current-mirror amplifiers. Specifically, by sharing the current I<sub>b2</sub> (for the left-half side) with N divided differential-input transistors  $[(I_1, M_1), (I_2, M_2), ..., (I_N, M_N)]$ , their outputs can be combined via N nested current mirrors with ratios  $[(1:K_1),(1:K_2)...(1:K_N)]$ . Since  $M_1$ - $M_N$  are located in the signal path, all of their transconductances, which contribute to  $\mathbf{G}_{\text{m,eff}}$ , are multiplied and customizable via choosing K1 to KN. To achieve high DC gain and GBW, more mirror stages and bigger ratios are preferred. To lower the noise, the largest amount of current can be allocated to the 1st mirror with a small K1. To enhance SR, most of the current can be assigned to the 2nd-last mirror with enlarged  $K_{N-1}$  and  $K_N$ . Indeed, the mirror stages and ratios are only limited by the PM and transistor mismatches. If a large  $C_L$  is imposed, PM is no longer the stability constraint. Any mismatches generate a voltage offset. Upsizing W and L of the DP amplifier transistors and mirrors improves matching and intrinsic gain. Both are important to the expected values of G<sub>m.eff</sub> and R<sub>out</sub>. Along such a NCM process, Rout is improved as well since less current goes to the output stage. Thus, the DC gain can be as high as that of a folded-cascode amplifier, but without the output swing penalty. Moreover, unlike the folded-cascode and current-mirror amplifiers, cutting the current of the output stage does not essentially degrade SR. In fact, as long as  $K_NI_N>I_{b2}$ , the SR of the NCM can still outperform that of the DP amplifier.

This work implements a 4-step NCM amplifier (Fig. 17.2.2) with the sub mirror ratios used for design flexibility. The total bias current (3µA) is divided into 60 unit currents (I<sub>II</sub>=50nA). On the right-half side, the DP amplifier transistors are split into M<sub>1</sub>-M<sub>4</sub>. Their outputs are summed via the mirrors realized by M<sub>5</sub>-M<sub>12</sub>.  $M_{13}$  collects the output of the left-half, to form the single-ended output with  $M_{12}$ . The analytical equations in Fig. 17.2.2 show how the mirror ratios  $K_1$  to  $K_7$ contribute to each performance metric. The DC gain is mainly given by  $2K_2K_4K_6/(K_3K_5)$ . This, together with  $K_7$ , roughly defines the GBW. Large  $K_{6.7}$  is set to enhance SR. The noise is a tradeoff under small  $K_1$  (and large  $K_2/K_1$ ), as the transistor's noise is also amplified by the mirror ratios. To leverage them, the 1st mirror  $M_5$ - $M_6$  uses a moderate ratio of 3 ( $K_1$ =2 and  $K_2$ =6). The  $2^{nd}$  mirror  $M_7$ - $M_8$ draws less current under a larger ratio of 4 (K<sub>3</sub>=1 and K<sub>4</sub>=4) to boost the DC gain and GBW, as they contribute negligible noise. The 3rd mirror Mg-M10 also uses a ratio of 4 (K<sub>5</sub>=2 and K<sub>6</sub>=8), but the given current is doubled to enhance SR. The  $4^{th}$  mirror  $M_{11}$ - $M_{12}$  is given the largest ratio ( $K_7$ =6) to benefit the SR and  $G_{m,eff}$ . Overall, the DC gain, GBW and SR are theoretically improved by 47.6dB, 48× and 1.8×, respectively, when compared to the DP amplifier. Though the noise voltage of NCM amplifier is 1.8× higher than that of the DP amplifier, it is still 1.44× better than that of the current-mirror amplifier under K=6 (equivalent to K<sub>7</sub> in Fig. 17.2.2).

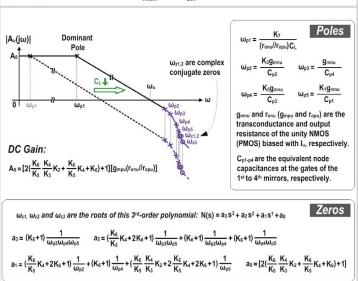

The multipath feedforward nature of NCM creates three left-half-plane (LHP) zeros,  $\omega_{z1}$  to  $\omega_{z3}$ , reducing the negative phase shift caused by the four non-dominant poles  $\omega_{p2}$  to  $\omega_{p5}$  (Fig. 17.2.3). Since  $\omega_{p2}\text{-}\omega_{p5}$  and  $\omega_{z1}\text{-}\omega_{z3}$  are all beyond the unity-gain frequency,  $\omega_{u}$ , the stability is unconditional during startup, large transients or saturation recovery. This fact differentiates it from explicit multipath feedforward compensation [5] that consumes extra power and is conditionally stable. Here, the stability is bounded by the light- $C_{l}$  condition.

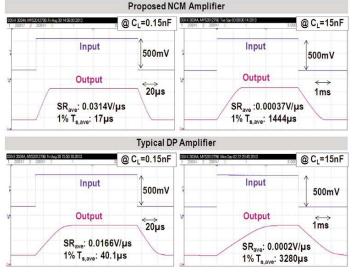

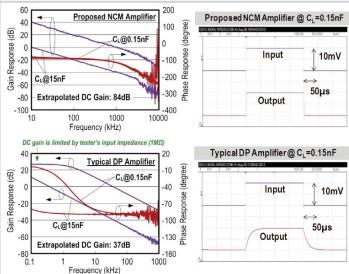

The NCM and DP amplifiers are fabricated in 0.18 $\mu$ m CMOS for comparison at equal power and area. Their measured AC and small-step responses are plotted in Fig. 17.2.4. The NCM shows 0.013-to-1.24MHz GBW, linearly scalable with C<sub>L</sub> from 15 to 0.15nF, which are >33× higher than those of the DP amplifier. The extrapolated DC gain (84dB) of the NCM amplifier also compares favorably with that (37dB) of the DP amplifier. The stability of the NCM amplifier is limited at the light-C<sub>L</sub> side (62.4° PM at 0.15nF C<sub>L</sub>). The large-step responses are plotted in Fig. 17.2.5. The chip summary and photos are given in Fig. 17.2.6. The NCM amplifier has better overall FOM<sub>1</sub> (>33×) and FOM<sub>2</sub> (>1.8×).

Comparing with the recent three-stage amplifiers of Fig. 17.2.7, this work shows the highest  $FOM_1$  (>6.6×), widest  $C_L$  drivability (>10×) and better stability (PM>62°). Before adopting any dynamic-biasing SR-enhancement technique [6],  $FOM_2$  is still 2.2× higher than [2], but 1.2 to 1.47× lower than [3], [4].

## Acknowledgements:

This work was funded by University of Macau MYRG, and Macao FDCT (015/2012/A1) and SKL fund.

## References:

- [1] C.-W. Lu, et al., "A 10-bit Resistor-Floating-Resistor-String DAC (RFR-DAC) for High Color-Depth LCD Driver ICs," *IEEE J. Solid-State Circuits*, vol. 47, pp. 2454-2466, Oct. 2012.

- [2] X. Peng, et al., "Impedance Adapting Compensation for Low-Power Multistage Amplifiers," *IEEE J. Solid-State Circuits*, vol. 46, pp. 445-451, Feb. 2011

- [3] S. Chong, et al., "Cross Feedforward Cascode Compensation for Low-Power Three-Stage Amplifier with Large Capacitive Load," *IEEE J. Solid-State Circuits*, vol. 47, pp. 2227-2234, Sep. 2012.

- [4] Z. Yan, et al., "A 0.016mm²  $144\mu$ W Three-Stage Amplifier Capable of Driving 1-to-15nF Capacitive Load with >0.95MHz GBW," ISSCC Dig. Tech. Papers, pp. 368-369, Feb. 2012.

- [5] A. Thomsen, et al., "A Five Stage Chopper Stabilized Instrumentation Amplifier Using Feedforward Compensation," *Symp. on VLSI Circuits, Dig. Tech. Papers*, pp. 220-223, Jun. 1998.

- [6] A. Martin, et al., "Low-Voltage Super Class AB CMOS OTA Cells with Very High Slew Rate and Power Efficiency," *IEEE J. Solid-State Circuits*, vol. 40, pp. 1068-1077, May 2005.

Figure 17.2.1: DP amplifier outperforms the Current-Mirror amplifier in terms of  $G_{m, \rm eff}$ , GBW, SR and noise, for any K. The NCM amplifier outperforms both by using the current to boost  $G_{m, \rm eff}$  and  $R_{\rm out}$ .

Figure 17.2.3: Bode plot of the 4-step NCM single-stage amplifier.

Figure 17.2.5: Measured large-step responses of the NCM (Upper) and DP (lower) amplifiers at equal power and area.

Figure 17.2.2: Implemented 4-step NCM single-stage amplifier.

Figure 17.2.4: Measured AC (left) and small-step (right) responses of the NCM and DP amplifiers at equal power and area.

|                                                  | Single-Stage Amplifiers   |              |                |                         |               |                |

|--------------------------------------------------|---------------------------|--------------|----------------|-------------------------|---------------|----------------|

| Die Photo                                        | Proposed NCM<br>Amplifier |              |                | Typical DP<br>Amplifier |               |                |

| Load C <sub>L</sub> (nF)                         | 0.15                      | 0.5          | 15             | 0.15                    | 0.5           | 15             |

| GBW (MHz)                                        | 1.24                      | 0.396        | 0.013          | 0.0371                  | 0.0116        | 0.00038        |

| Phase Margin (degree)                            | 62.4                      | 81.4         | 90.2           | 91.7                    | 92.5          | 92.9           |

| Gain Margin (dB)                                 | 15.9                      | 23.7         | 56.1           | >60                     | >60           | >60            |

| SR <sub>ave</sub> (V/µs)                         | 0.0314                    | 0.0115       | 0.00037        | 0.0166                  | 0.0058        | 0.0002         |

| 1% T <sub>s.ave</sub> (μs)                       | 17                        | 47.1         | 1444           | 40.1                    | 109           | 3280           |

| DC Gain (dB) (extrapolated)                      | 84                        |              |                | 37                      |               |                |

| Input-Referred Noise (nV/√Hz)                    | 1470 @<br>0.1kHz          | 440@<br>1kHz | 140 @<br>10kHz | 680 @<br>0.1kHz         | 270 @<br>1kHz | 106 @<br>10kHz |

| Power (µW) @ V <sub>DD</sub> (V)                 | 3.6 @ 1.2                 |              |                | 3.6@1.2                 |               |                |

| Chip Area (mm²)                                  | 0.0013                    |              |                | 0.0013                  |               |                |

| CMOS Technology                                  | 0.18µm                    |              |                | 0.18µm                  |               |                |

| FOM <sub>1</sub> [(MHz·pF)/µW/mm <sup>2</sup> ]  | 39,744                    | 42,308       | 41,667         | 1,189                   | 1,239         | 1,218          |

| FOM <sub>2</sub> [(V/µs·pF)/µW/mm <sup>2</sup> ] | 1,006                     | 1,229        | 1,186          | 532                     | 620           | 641            |

Figure 17.2.6: Comparison of NCM and DP amplifiers under the same power and area.

## **ISSCC 2014 PAPER CONTINUATIONS**