# A 3µm CMOS ANALOGUE-DIGITAL INTEGRATED CIRCUIT FOR PORTABLE RADIOTELEPHONES

Rui Martins<sup>1</sup>. João Vital<sup>1</sup>, Palma Martins<sup>2</sup>

Jorge Guilherme<sup>3</sup>, Carlos Neta<sup>4</sup>, Ernesto Alverca<sup>4</sup>, José Franca<sup>1</sup>

1- Instituto Superior Técnico (IST)

2- Depósito Geral de Material de Transmissões (DGMT)

3- Instituto Tecnológico para e Europa Comunitária (ITEC)

4- Empresa de Investigação e Desenvolvimento de Electrónica (EID)

#### ABSTRACT

This paper describes the design of a 3µm CMOS integrated circuit for a portable radiotelephone. The circuit performs the signal processing functions required for the speech channel and signalling, and also incorporates a programmable power saving control circuitry. Both analog and digital techniques have been employed to reduce the silicon area taken up by the chip and its overall power consumption, as well as to minimize the number of external components.

#### 1. INTRODUCTION

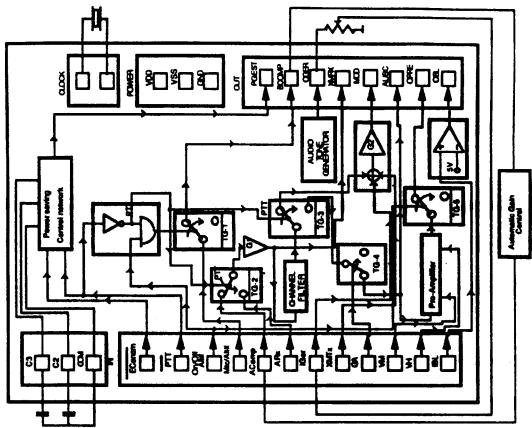

Integrated circuits (IC's) for portable radiotelephones (PRT's) have to meet stringent specifications in comparison to their line-fed counterparts, namely with respect to the low current consumption which is essential to save the lifetime of the battery [1-3]. A large dynamic range is also necessary to mantain a good signal-to-noise ratio in a noisy environment. The IC's for this type of application are usually required to perform such functions as automatic gain-controlled (AGC) amplification, filtering, output signal amplification, buffering and sub-audio tone generation. In addition, such IC's also incorporate a programmable power saving control circuitry which is essential to extend the operating lifetime. The overall architecture of the IC incorporating all the above functions is shown in the block diagram of Fig.1.

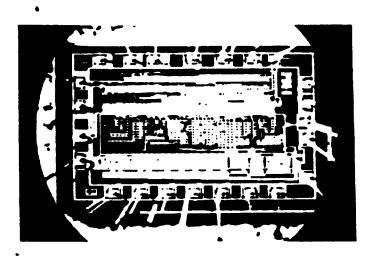

The IC corresponding to the architecture of Fig. 1 has been integrated using a  $3\mu$ m analogue CMOS process where we utilized extensively switched-capacitor (SC) techniques [4] to realise the analogue functions (the AGC has not been included in the 1st. prototype version). The photomicrograph of the prototype chip is shown in Fig. 2. In the following sections we shall describe the design of some of the most relevant circuit building blocks that have been employed in such an application.

Fig. 1: Block diagram of the IC architecture for a portable radiotelephone application.

Fig. 2: Photomicrograph of the prototype IC.

## 2. AUDIOBAND SIGNAL PROCESSING FUNCTIONS

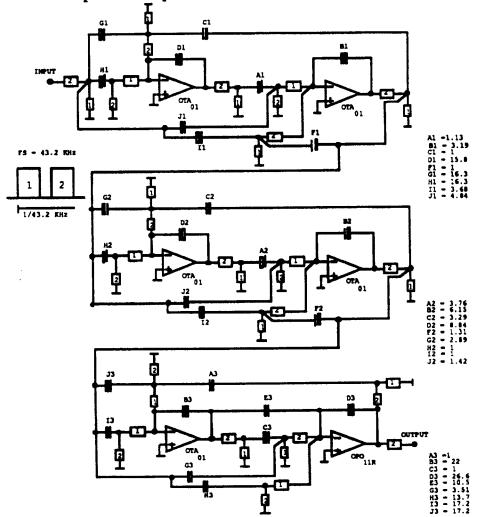

The audioband signal processing functions include a channel filter and an automatic gain-controlled amplifier. The channel filter is a 6th. order elliptic bandpass filter realised as a cascade of SC biquadratic sections, as illustrated in the schematic representation of Fig.3. The amplitude response of this filter determines the passband from 300Hz to 3000Hz, with a maximum ripple of 0.5dB, together with a lower stopband giving a minimum attenuation of 30 dB at 150Hz, and an upper stopband giving a minimum attenuation of 33dB at 6000Hz. The design of the filter has been optimized in order to achive maximum signal handling capablity and minimise the capacitance spread and total area.

Fig. 3: Channel filter using a cascade of SC biquads.

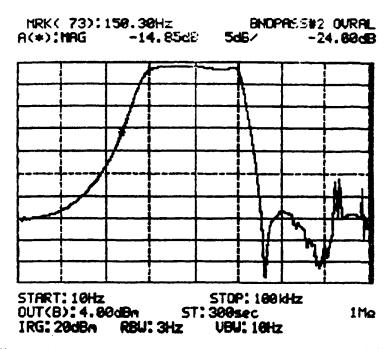

The overall experimental response of the filter, shown in Fig. 4, is according to the specifications, except for the minimum attenuation in the lower stopband which is above the designed value. A careful investigation of the circuit indicated that this problem is due to a design error which affected one transmission zero nominally placed at 123Hz (a new design solution has already been adopted to overcome this difficulty).

Fig. 4: Measured amplitude response of the channel filter.

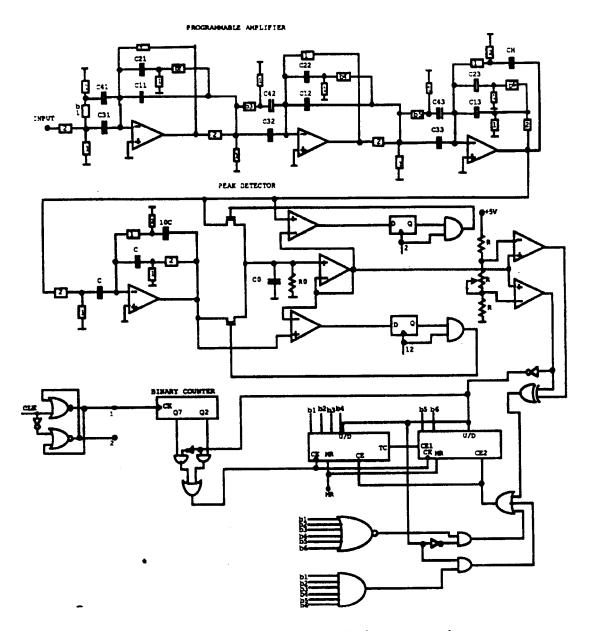

The gain-programmable amplifier is realised using a cascade of three SC amplifiers, as illustrated in Fig. 5. Overall, the circuit provides a total of six branches to control the gain. Thus, for a maximum of  $2^6 = 64$  steps, the resulting dynamic range is 40dB and the minimum programming step is 0.7dB. Following the gain-programmable SC amplifier, there is a peak detector and an inverting SC amplifier. The function of the inverting amplifier is to allow the peak detector to operate in both positive and negative input signals, and thus minimise the effect of the offset of the amplifier. The output of the peak detector drives a window comparator which controls the up-down counter. When the signal is inside the window the counter is enabled, whereas when the signal lies outside the window the counter moves in the appropriate direction in order to either reduce or enlarge the signal level and thus bringing it into the window.

Fig. 5: Analog-digital network for automatic gain-controlled amplification.

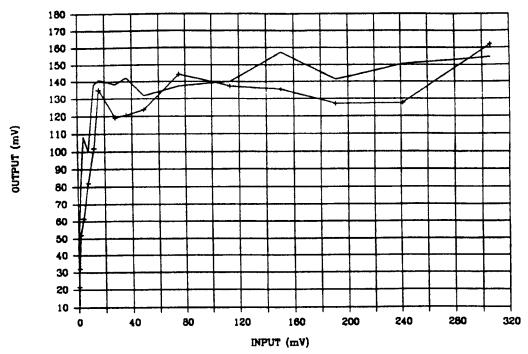

The two logic gates inhibit the counter when this is either at the bottom or at the top of the counting sequence. In this manner we prevent the incremental step from the top to the bottom of the scale which could make the circuit to oscilate. Such an AGC amplifier was built as a discrete component model to verify its funcionality. The experimental evaluation of this model demonstrated the correct operation of the circuit which leads to the type of transfer characteristics illustrated in Fig. 6.

Fig. 6: Measured transfer characteristics of the AGC amplifier.

## 3. SUB-AUDIO TONE GENERATOR

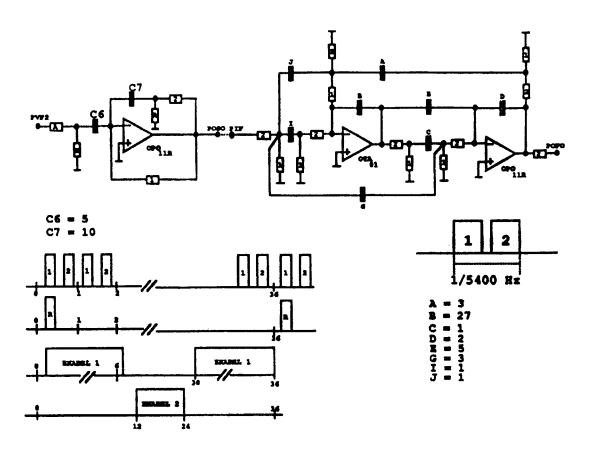

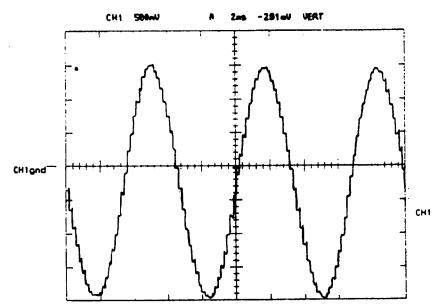

For the implementation of the 150Hz tone generator, we employed a trapezoidal waveform generator followed by a 2nd. order lowpass SC filter. The trapezoidal generator is realised by means of an SC integrator, with both positive and negative gains, controlled by the waveforms shown in Fig.7, together with the schematic representation of the circuit. The 150Hz trapezoidal waveform is generated by a sequence of 36 samples produced at a rate of 5400Hz. In the first 12 samples, the integrator generates a positive ramp with an incremental step of 125mV up to a maximum level of 750mV. Then, during the next six samples, the signal is held constant at 750mV. At the end of this period, the integrator starts generating a negative ramp with a slope of -125mV per step. After 12 steps, the signal level reaches -750mV and then is held constant during the following 6 samples. The 5th. harmonic (750Hz) of the waveform shaped in this way is attenuated by about 33dB by the lowpass filter. This is good enough for the purpose of this application. From cycle to cycle there is a reset operation to reduce the effects of the offset voltage of the amplifier. The lowpass section introduces a voltage gain of 9.54dB to scale the signal level to 2.25V. The experimental results obtained for the sub-audio tone generator are shown in Fig.8.

Fig. 7: SC network and switching waveforms for sub-audio tone generation.

Fig. 8: Sinusoidal waveform at the output of the sub-audio tone generator.

### 4. POWER SAVING CONTROL NETWORK

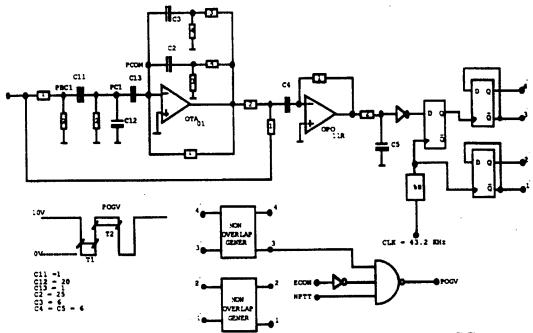

The power saving control network, whose schematic diagram is illustrated in Fig.9, is realised using an SC integrator which provides two time constants whose values are determined by appropriate SC feedback branches controlled by a comparator and a flip-flop.

Fig. 9: Power saving control network employing an SC time-descriminating circuit.

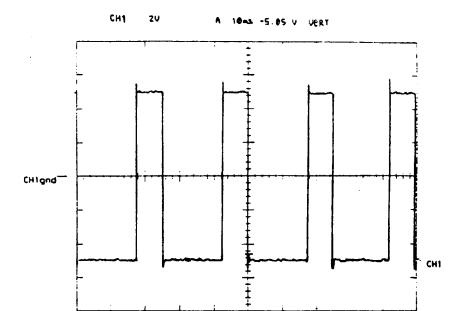

Each one of these time constants define the ON and OFF time intervals of the waveform, and therefore make it possible to control the duty-cycle of the oscilator. The input branch of the integrator comprises a T of capacitors to reduce the capacitance spread. The external capacitors which allow the modification of the time constants are connected to nodes PBC1, PC1 and PCON. When one feedback capacitor branch of the integrator is active, the other one remains discharged until the output signal of the integrator reaches the reference voltage at the input of the comparator. At that time, the comparator changes the output state and the charged capacitor is discharged. Then, the other feedback capacitor branch starts operating until the output signal of the integrator reaches the reference voltage. In this manner, we can control independently the ON and OFF time intervals of the waveform employed for power saving control. Some experimental results of the operation of this network are illustrated in Fig. 10.

Fig. 10: Experimental output waveform of the power saving control network.

## 5. CONCLUSIONS

We described a 3µm CMOS integrated circuit which comprises the signal processing and control functions required for the audio unit of a portable radiotelephone. The signal processing functions include audio channel filtering, sub-audio tone generation, automatic gain control, and signal amplification. A power saving control circuitry was also included to allow extended battery-fed operation of the circuit. Those circuits were designed employing mixed analog and digital techniques to reduce the silicon area taken up by the chip as well as its overall power consumption, and also minimise the number of external components. Overall, the prototype IC's performed according to the specifications.

#### REFERENCES

- [1] G. Melcher and al., "A 3 \mu m CMOS Analog Audio Circuit for Mobile Telephone Applications", in Proceedings ESSCIRC 89, Sept. 1989.

- [2] P. Consiglio et al., "Fully Line-Fed Hands-Free Telephone Set", in Proceedings ESSCIRC 87, Sept. 1987.

- [3] E. Moons, et al., "Fully Integrated Analog Telephone", in Proceedings ESSCIRC 88, Sept. 1988.

- [4] R. Gregorian, G. Temes, "Analog Integrated Circuits for Signal Processing", Wiley, New York, 1986.