# A $2.4\mu m$ CMOS SWITCHED-CAPACITOR VIDEO DECIMATOR WITH SAMPLING RATE REDUCTION FROM 40.5 MHZ TO 13.5 MHZ

#### **R.P.Martins**

#### J.E.Franca

Centro de Electrónica Aplicada da Universidade Técnica de Lisboa Departamento de Engenharia Electrotécnica e de Computadores Instituto Superior Técnico Avª Rovisco Pais, 1096 Lisboa Codex, Portugal

## **Abstract**

This paper describes the design and integrated circuit implementation of a 5-th order elliptic lowpass Switched-Capacitor (SC) video decimator with a cut-off frequency of 3.6MHz and sampling rate reduction from 40.5MHz to 13.5MHz. A recently proposed novel decimator architecture is employed to make the settling time requirements of the operational amplifiers similar to those of a conventional SC filter with switching frequency of only 13.5MHz. The circuit is implemented using a 2.4µm CMOS double-poly process yielding a total area of less than 1mm². The power consumption is less than 50mW with 10V power supply.

#### 1. INTRODUCTION

In recent years, significant research efforts have been devoted worldwide to the design of Switched-Capacitor (SC) circuits and systems for applications in video signal processing and high speed data transmission, e.g. [1,2]. Multirate SC networks have a great potential for such applications, specially for those that require a filtering function together with the alteration of the sampling rate [3,4]. SC decimators with Infinite Impulse Response [IIR) transfer functions constitute an important class of such circuits, mainly because of their ability to produce highly selective amplitude responses at minimum hardware cost. Until recently, however, IIR SC decimators have been designed in a non-optimum fashion whereby the operational amplifiers (OA's) have to operate at the higher sampling rate at the input of the decimator, as it happens in conventional SC filters, thus restricting the range of applications at high-frequency.

Recent advances in multirate SC networks led to the development of optimum IIR SC decimators which efficiently reduce the speed requirements of the OA's, as well as the capacitance spread and total capacitor area. In this class of circuits, we have presently available 1st. and 2nd. order building blocks [5,6] which can be cascaded to realize higher order transfer functions [7]. However, for such applications it is more efficient to consider the design of an N-th order building block which is capable of producing arbitrary passband and anti-aliasing amplitude responses using more economical circuits [8]. Based on this type of architecture, we present in this paper the design and integrated circuit implementation of an SC decimator suitable for video applications according to the CCITT recommendations [9,10]. An efficient circuit topology is adopted yielding rather low values of the capacitance spread (8) and total capacitor area (less than 100), as well as reduced response degradation under non-ideal characteristics of the OA's. The circuit employs high frequency OA's with 70dB DC-Gain and 100MHz Gain-Bandwidth (GBW) product (the phase margin is 55°, with 1pF capacitive load), and which can settle in much less than the maximum time of 34ns allowed by the switching waveforms. The circuit, which is implemented

in a 2.4 $\mu$ m CMOS double-poly process [11], occupies a total area of less than 1mm<sup>2</sup> and consumes less than 50mW with 10V power supply.

# 2. 5-th ORDER SC LOWPASS VIDEO DECIMATOR

The SC lowpass video decimator considered in this paper is designed to reduce the sampling rate from  $3F_{\rm S}{=}40.5 \text{MHz}$  to  $F_{\rm S}{=}13.5 \text{MHz}$  (M=3), and possesses a 5th. order elliptic lowpass frequency response with passband ripple of 0.2dB, cut-off frequency  $F_{\rm C}{=}3.6 \text{MHz},$  and minimum 35dB rejection above 4.44MHz [9,10].

Modified Z-Transfer Function: Based on a computer aided filter synthesis tool [12], we obtained the bilinear discrete-time coefficients given in Table 1 for the original Z-transfer function of the decimator prototype filter that can be expressed as

$$H(z) = k \frac{\left[\prod_{i=1}^{2} (1 - 2r_{0_{i}} \cos(\theta_{0_{i}}) \cdot z^{-1} + r_{0_{i}}^{2} \cdot z^{-2})\right] \cdot [1 + z^{-1}]}{\left[\prod_{i=1}^{2} (1 - 2r_{P_{i}} \cos(\theta_{P_{i}}) \cdot z^{-1} + r_{P_{i}}^{2} \cdot z^{-2})\right] \cdot [b_{0} - z^{-1}]}$$

(1)

where the unit delay period corresponds to the sampling period of  $1/3F_S$  at the input of the decimator. The zeroes and poles of the 2nd. order sections are represented by polar coordinates  $r_{O(P)i}$  and  $\theta_{O(P)i}$ , whereas the pole of the 1st. order section is represented by  $b_O$ . The modified Z-tansfer function for optimum implementation of this SC decimator can be written as [6]

$$\frac{\sum_{m=0}^{15} \overline{a}_{m} \cdot z^{-m}}{\left[\prod_{i=1}^{2} (1-2r_{p_{i}}^{3} \cos(3\theta_{p_{i}}) \cdot z^{-3} + r_{p_{i}}^{6} \cdot z^{-6})\right] \cdot [b_{0}^{3} - z^{-3}]}$$

(2)

where the unit delay period still corresponds to 1/3F<sub>s</sub>. For unity DC-gain, the resulting modified discrete-time coefficients are given in Table 2.

so coefficients are given in Table 2.

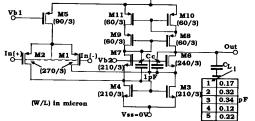

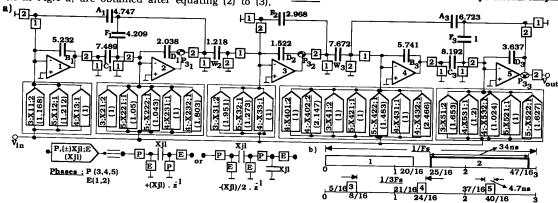

SC Circuit: To implement the above modified Z-transfer function, we arrived at the SC decimator circuit shown in Fig.1-a, which operates with the switching waveforms of Fig.1-b. This circuit topology has been selected in order to obtain low capacitance spread and total capacitor area, and also reduced response degradation under non-ideal characteristics of the OA's [8]. Following the procedure presented in [8] the circuit can be described by the following Z-transfer function

$$T(z) = \frac{V_{out} = V_{3}}{V_{in}}(z) = \frac{k_{3}}{D_{3}(z)} \cdot [N_{3l_{3}}(z) + W_{3}(z) \cdot N_{32_{3}}(z) \cdot \frac{V_{3}}{V_{in}}(z)]$$

(3-a)

with

$$\frac{v_{3_{2}}}{v_{in}}(z) \cdot \frac{k_{2}}{D_{2}(z)} \cdot \left\{N_{31_{2}}(z) + W_{2}(z) \cdot N_{32_{2}}(z) \cdot (k_{1} \cdot \frac{N_{31_{1}}(z)}{D_{1}(z)})\right\}$$

(3-b)

The terms  $k_1$ ,  $D_1(z)$ ,  $N_{311}(z)$  and  $N_{321}(z)$  are associated with the Z-transfer function of each section and Wi(z) is the equivalent Z-transfer function of the coupling section. For the 2nd. order sections [6,8] the constant coefficient is given by

$$k_{1(3)} = \frac{1}{(1+F_{1(3)})}$$

(4-a)

whereas the numerator polynomial functions are expressed as

$$N_{31_{1(3)}}(z) = B_{1(3)}X_{2(5)}(z) \cdot [1-z^{-3}] - C_{1(3)}X_{1(4)}(z)$$

(4-b)

$$N_{32_{1(3)}}(z) = -C_{1(3)}$$

(4-c)

and, for the denominator polynomial functions, we have  $D_{1(3)}(z) = [1 + \beta_{1(3)} z^{-3} + \gamma_{1(3)} z^{-6}]$

whose terms  $\beta_{1(3)}$  and  $\gamma_{1(3)}$  are given by

$$\beta_{1(3)} = \frac{A_{1(3)} C_{1(3)}^{-1} B_{1(3)} D_{1(3)}^{-1} (1+B_{1(3)} D_{1(3)}^{-1} + B_{1(3)}^{-1} F_{1(3)})}{B_{1(3)} (D_{1(3)} + F_{1(3)})}$$

(4-e)

$$\begin{split} \beta_{1\,(3)} &= \frac{A_{1\,(3)}\,C_{1\,(3)}\,-B_{1\,(3)}\,D_{1\,(3)}\,\left(1+B_{1\,(3)}\,D_{1\,(3)}\,+B_{1\,(3)}\,F_{1\,(3)}\right)}{B_{1\,(3)}\,\left(D_{1\,(3)}\,+F_{1\,(3)}\right)} \\ \gamma_{1\,(3)} &= \frac{B_{1\,(3)}\,D_{1\,(3)}}{B_{1\,(3)}\,\left(D_{1\,(3)}\,+F_{1\,(3)}\right)} \end{split} \tag{4-e}$$

For the 1st. order section [6,8] we have the constant coefficient (5-a)

the numerator polynomial functions

$$N_{31_2}(z) = X_{31}(z) = X_{30} + X_{31}z^{-1} + X_{32}z^{-2} + X_{33}z^{-3}$$

(5-b)

$$N_{32_2}(z) = 1$$

(5-c)

and, the denominator polynomial function

$$D_{2}(z) = [(D_{2} + F_{2}) - D_{2}z^{-3}]$$

(5-d)

Finally, for the coupling sections [6,8] we have

$$W_{2(3)}(z) = W_{2(3)} \cdot z$$

(6)

$W_{2(3)}(z) = W_{2(3)} \cdot z^{-3}$  (6) In the above expressions, the terms  $X_{jl}(z)$  of the numerator polynomial functions represent the equivalent transfer functions of the input SC branches, where j is the order of the OA in the circuit and I the order of the coefficient (example:  $X_{32}$  is the coefficient of  $z^{-2}$  in the input capacitor set of OA 3).

The final normalized capacitance values, which are also given in Fig.1-a, are obtained after equating (2) to (3),

and scaling for maximum signal handling. An optimising procedure has also been employed to minimise the capacitance spread and total capacitor area in the circuit yielding, respectively, 8 and less than 100 units.

| Numerator                               |                     | Denominator                                                                    |                  |                      |            | Table 1: Bilinear       |                   |  |

|-----------------------------------------|---------------------|--------------------------------------------------------------------------------|------------------|----------------------|------------|-------------------------|-------------------|--|

| <u>k</u>                                | .022698             | 2r <sub>p,</sub> cos(                                                          | θ <sub>h</sub> ) | 1.4887               | <b>760</b> | _                       | discrete-time     |  |

| 2r <sub>01</sub> cos( 9 <sub>01</sub> ) | 1.519196            | P <sub>1</sub><br>2r <sub>p<sub>2</sub></sub> cos(θ <sub>p<sub>3</sub></sub> ) |                  |                      |            | coefficients of the     |                   |  |

| r2,                                     | 1                   |                                                                                |                  |                      |            | 5th. order SC decimator |                   |  |

| 2racos(ga)                              | 1.133340            |                                                                                |                  |                      |            |                         |                   |  |

| 2 2                                     | 1.133340            | T <sub>2</sub>                                                                 |                  | .922218              |            |                         |                   |  |

| r <sub>02</sub>                         | 1                   | bo                                                                             |                  | 1.4342               | 09         | pr                      | ototype filter.   |  |

| Numerator                               |                     |                                                                                | Denominator      |                      |            | Or .                    | 1                 |  |

| ª0 .0669623                             | 8 474               | 4776 2r                                                                        | <u> </u>         | os(30 <sub>P</sub> ) |            |                         |                   |  |

| a1 .1434827                             | <sup>2</sup> 9 .424 | 9211                                                                           | 1                |                      | -          |                         | Table 2:          |  |

| <sup>a</sup> 2 .2032289                 |                     |                                                                                | Þ                | 1                    | 326        | 32457                   | Table 2.          |  |

| a3 .2925909                             |                     |                                                                                | 3 .              | 00(38 <sub>E</sub> ) | 28         | 4706                    | Coefficients      |  |

| 4.3759253                               |                     | 1566                                                                           | 2 6              |                      |            |                         | of the Eth anda-  |  |

| 5.4316805                               |                     |                                                                                | Þ                |                      | 784        | 3341                    | of the 5th. order |  |

| a6 .4950802                             |                     |                                                                                | b                | 3                    | 0 0 5      | 0105                    | SC decimator.     |  |

| <sup>2</sup> 7.5151721                  | <b>2</b> 15 .013    | 1211                                                                           |                  | •                    | e.90       | ~109                    |                   |  |

## 3. IC IMPLEMENTATION

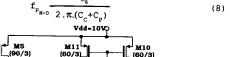

Operational Amplifiers: For the SC decimator circuit shown in Fig.1, we have designed an high-speed single-ended folded cascode OA whose structure is shigher-ended to the case of the whose structure is shown in Fig.2. To obtain a fast settling time we use a well known technique [10,13] which employs two compensating capacitors  $C_{\rm C}$  together with the output capacitor  $C_{\rm L}$ . The pole and zero frequencies of the amplitude response are given by

$$f_{p_0} = \frac{g_{0_6}}{2 \pi C} \tag{7}$$

for the dominant pole, by

Fig. 2: CMOS circuit structure of the Operational Amplifier.

Fig.1: 5th. order SC Video Decimator (M=3, Fsin=40.5MHz, Fsout=13.5MHz, Fcutoff=3.6MHz, Ripple=0.2dB). a) Circuit. b) Switching Waveforms.

for the first non-dominant pole, and by

$$f_z = \frac{g_{m_6}}{C_C} \tag{9}$$

for the zero. The parameters  $g_{06}$ ,  $g_{m6}$  and  $C_P$  are, respectively, the output conductance, the transconductance and the parasitic capacitance at the source node of cascode transistor  $M_6$ . If  $C_P << C_C$ , then the zero compensates for the first non--dominant pole and the settling time will be imposed by another non-dominant pole at a much higher frequency. In Fig.3 we present results of the electrical simulation of the OA using the ELDO program [14]. The amplitude and phase responses (Fig.3-a) show a DC-Gain=70dB and a value of GB=100MHz (phase margin,  $\phi_m \approx 57^{\circ}$ ) with  $C_C=1PF$  and  $C_L=1.3pF$  (maximum OA capacitive load in the circuit). For a unity gain configuration, and input voltage step of 1V, the settling-time is 17ns (Fig.3-b). The DC transfer characteristic of the amplifier is presented in Fig.3-c showing an output voltage swing of 6V:

To maximise the settling times of the amplifiers in the circuit we have appropriatelly tailored the values of the output compensating capacitors  $C_L$  in the circuit, according to the capacitive loads of each OA in each switching phase. Thus, OA's which have larger output capacitive loads (OA's 1 and 4) will have smaller values of  $C_L$ , whereas OA's with smaller output capacitive loads (OA's 2.3 and 5) will have larger values of  $C_L$ .

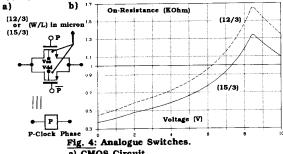

Analogue Switches: For very high speed of operation together with reduced charge injection and clock feedthrough, we have adopted the structure of Fig.4-a to realise the analogue switches in the SC decimator of Fig.1. The transistors in the input polyphase networks have larger (W/L) ratios than in the recursive network, since they must supply more current in larger capacitors and switch in time intervals of only 4.7ns. The on-resistance, evaluated with ELDO [14], Fig.4-b, is  $R_{on}\approx700\Omega$  (W/L=15/3) and  $R_{on}\approx900\Omega$  (W/L=12/3) for the circuit operating voltage (around 5V). These values imply time constants of  $\tau_1\approx0.5$ ns (C≈0.1pF), in the input polyphase networks, and of  $\tau_2\approx5$ ns (C≈1pF) in the

polyphase networks, and of  $\tau_2{\approx}5\text{ns}$  (C=1pF) in the recursive network.

a) CMOS Circuit.b) Simulated On-Resistance.

<u>Capacitors</u>: High precision capacitors have been designed with guard rings around the top plate in order to minimise etching and fringing effects. To maximise the accuracy of larger capacitance ratios, we employ an association of unit capacitors (unity capacitance is approximately  $0.1 pF=18x18\mu m^2$ ), and to prevent high-frequency parasitic signal injection into the analog path through the substrate the overall set of capacitors is shielded using an N-well substrate connected to ground.

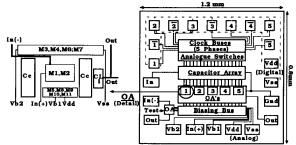

Chip Architecture The SC video decimator has been implemented as an integrated circuit using a 2.4µm CMOS, N-well, double-poly, single-metal technology [11]. The layout architecture of the chip is presented in Fig.5. Special cares have been taken into account in order to reduce parasitic high-frequency signal injection in the analog path, clockfeedthrough and capacitance overlap bettween the outputs and inverting inputs of the OA's. Different analog and digital power supplies are provided to decouple the analog part of the circuit (OA's and Capacitors) from the digital part (Switches). The clock busses are separated from the rest of the circuit and independent power supply voltages are also supplied to bias all the OA's.

Fig. 5: Integrated Circuit Architecture.

# 4. COMPUTER SIMULATED RESULTS

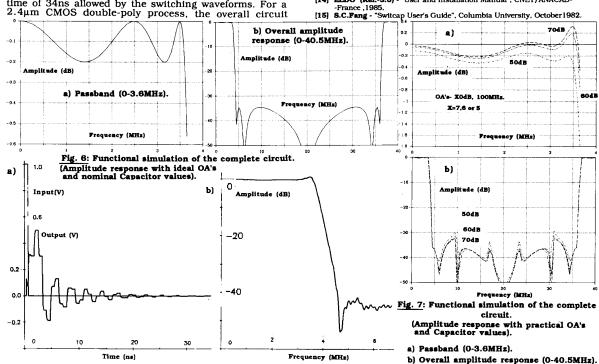

Functional Simulation: For ideal OA's and nominal capacitance values, the SC decimator of Fig.1 produces the computer simulated [15] passband and overall amplitude responses illustrated in Fig.6. In Fig.7 we can observe the resulting deviations of the amplitude responses when we consider practical 100MHz OA's with varying DC-Gain, together with realistic capacitance ratio accuracies of 0.1%. These results show an acceptable circuit performance for 100MHz OA's with DC-Gain values over 60dB, whereas for smaller DC-Gain values there is a visible degradation specially in the anti-aliasing-band.

Electrical Simulation: The electrical simulation of the circuit, which is carried-out using ELDO, is performed into two steps using appropriate macromodels for the amplifiers (DC-Gain=70dB, GB=100MHz, Slew rate=10V/ns) and switches(R  $_{\!on}$  =0.75K  $\!\Omega$  ). In the first step, we obtain the impulse response of the circuit by means of a transient analysis obtained for a 1V-step input voltage (Fig.8-a). Then, with an FFT post-processor, we obtain the amplitude frequency response illustrated in

# 5. CONCLUSIONS

In this paper we describe the design and integrated circuit implementation of a 5-th order elliptic lowpass SC video decimator, with cut-off frequency of 3.6MHz and sampling rate reduction from 40.5MHz to 13.5MHz. This is based on a novel decimator architecture which considerably relaxes the speed requirements of the amplifiers, and also minimises the capacitance spread and total capacitor area. The circuit employs high performance OA's with 70dB DC-Gain and 100MHz GB product, and which can settle in less than the maximum time of 34ns allowed by the switching waveforms. For a 2.4µm CMOS double-poly process, the overall circuit

occupies less than 1mm2 of silicon area, and consumes less than 50mW with 10V power supply.

Acknowledgements: We are grateful to Dr. Mohamed Tawfik and Dr.Larry Moore of Anacad-France for useful discussions and permission to use the electrical simulator ELDO.

- K.Nakayama, Y.Kuraishi "Present and Future Applications of Switched-Capacitor Circuits" IEEE Circuits and Devices Magazine, pp.10-21,

- P.Senn.M.S.Tawiik "Concepts for the restitution of Video Signals using

- P.Senn, M.S.Tawfik "Concepts for the restitution of Video Signals using MOS Analog Circuits" "Concepting international Symposium on Circuits and Systems 1988, [Helsinki, Finland], pp. 1935-1938, June 1988.

J.E.Franca "Non-Recursive Polyphase Switched-Capacitor Decimators and Interpolators" EEE Transactions on Circuits and Systems, vol. CAS-32, No.9, pp.877-887, September 1985.

J.E.Franca "IIR Switched-Capacitor Decimators and Interpolators with Biquad-Polyphase Structures" Proceedings 29th. Midwest Symposium on Circuits and Systems, pp.797-800, Lincoln, Nebraska, U.S.A., August 1986.

J.E.Franca, D.G.Haigh "Optimum Implementation of IIR Switched-Capacitor Decimators" Proceedings International Symposium on Circuits and Systems 1987, (Philadelphia, U.S.A.), pp.76-79, May 1987.

J.E.Franca, R.P. Martins "IIR Switched-Capacitor Decimator Building Blocks with Optimum Implementation" to appear in IEEE Transactions on Circuits and Systems.

R.P. Martins, J.E.Franca "Optimum Implementation of a Multistage IIR SC Bandpass Decimator for a Voiceband Analogue Interface System" Proceedings International Symposium on Circuits and Systems.

- Proceedings International Symposium on Circuits and Systems 1988, [Helsinki, Finland), pp. 1661-1664, June 1988.

R.P. Martins, J.E. Franca "A Novel N-th order IIR Switched-Capacitor Decimator building block with optimum implementation" Proceeding: International Symposium on Circuits and Systems, (Portland, Oregon, U.S.A.). May 1989.

- International Symposium on Circuits and Systems, [Portland, Oregon, U.S.A.), May 1989.

[9] CCIR XVth. Plenary Assembly, Vol. XXI-1-Broadcasting Service [Television], Geneva 1982.

[10] M.S.Tawfik, P.Senn "A 3.6-MHz Cutoff Frequency CMOS Elliptic Low-Pass Switched-Capacitor Ladder Filter for Video Communication" IEEE Trans. on Circuits and Systems, vol. SC-22, No.3, pp.378-384. June 1987.

[11] INVOMEC (https://orego.) 2.4 and 3 micron, double poly, double metal, N-Well CMOS process, Revision 6, Leuven-Belgium, 1st. April 1987.

[12] G.Szentirmai "S/FiltsYN Quick Reference Manual", April 1983.

[13] D.Ray, J.Gorechi "Novel single-ended CMOS transconductance amplifiers" Electronics Letters, vol. 21, No.15, pp.642-643, July 18, 1985.

[14] ELDO (Rel.-3.0) "User and Installation Manual", CNET/ANACAD-France, 1985.

Fig. 8: Eletrical Simulation of the complete circuit. a) Impulse Response. b) Amplitude Response